CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

Document #: 38-08032 Rev. *L Page 46 of 62

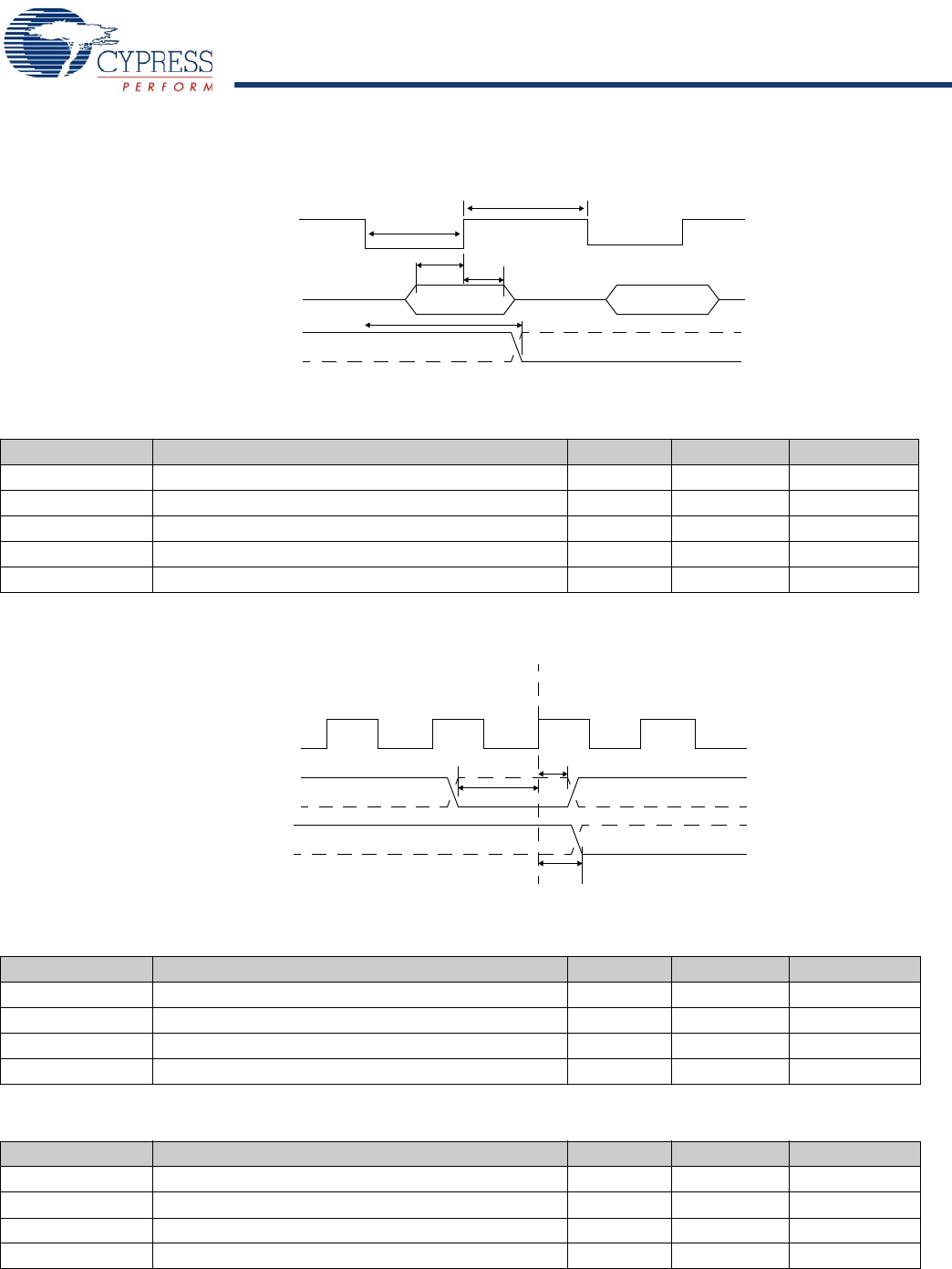

10.10 Slave FIFO Asynchronous Write

Figure 21. Slave FIFO Asynchronous Write Timing Diagram

[20]

10.11 Slave FIFO Synchronous Packet End Strobe

Figure 22. Slave FIFO Synchronous Packet End Strobe Timing Diagram

[20]

DATA

t

SFD

t

FDH

FLAGS

t

XFD

SLWR/SLCS#

t

WRpwh

t

WRpwl

SLWR

Table 25. Slave FIFO Asynchronous Write Parameters with Internally Sourced IFCLK

[23]

Parameter Description Min Max Unit

t

WRpwl

SLWR Pulse LOW 50 ns

t

WRpwh

SLWR Pulse HIGH 70 ns

t

SFD

SLWR to FIFO DATA Setup Time 10 ns

t

FDH

FIFO DATA to SLWR Hold Time 10 ns

t

XFD

SLWR to FLAGS Output Propagation Delay 70 ns

FLAGS

t

XFLG

IFCLK

PKTEND

t

SPE

t

PEH

Table 26. Slave FIFO Synchronous Packet End Strobe Parameters with Internally Sourced IFCLK

[21]

Parameter Description Min Max Unit

t

IFCLK

IFCLK Period 20.83 ns

t

SPE

PKTEND to Clock Setup Time 14.6 ns

t

PEH

Clock to PKTEND Hold Time 0 ns

t

XFLG

Clock to FLAGS Output Propagation Delay 9.5 ns

Table 27. Slave FIFO Synchronous Packet End Strobe Parameters with Externally Sourced IFCLK

[21]

Parameter Description Min Max Unit

t

IFCLK

IFCLK Period 20.83 200 ns

t

SPE

PKTEND to Clock Setup Time 8.6 ns

t

PEH

Clock to PKTEND Hold Time 2.5 ns

t

XFLG

Clock to FLAGS Output Propagation Delay 13.5 ns

[+] Feedback [+] Feedback