CYDC256B16, CYDC128B16,

CYDC064B16, CYDC128B08,

CYDC064B08

Document #: 001-01638 Rev. *E Page 15 of 26

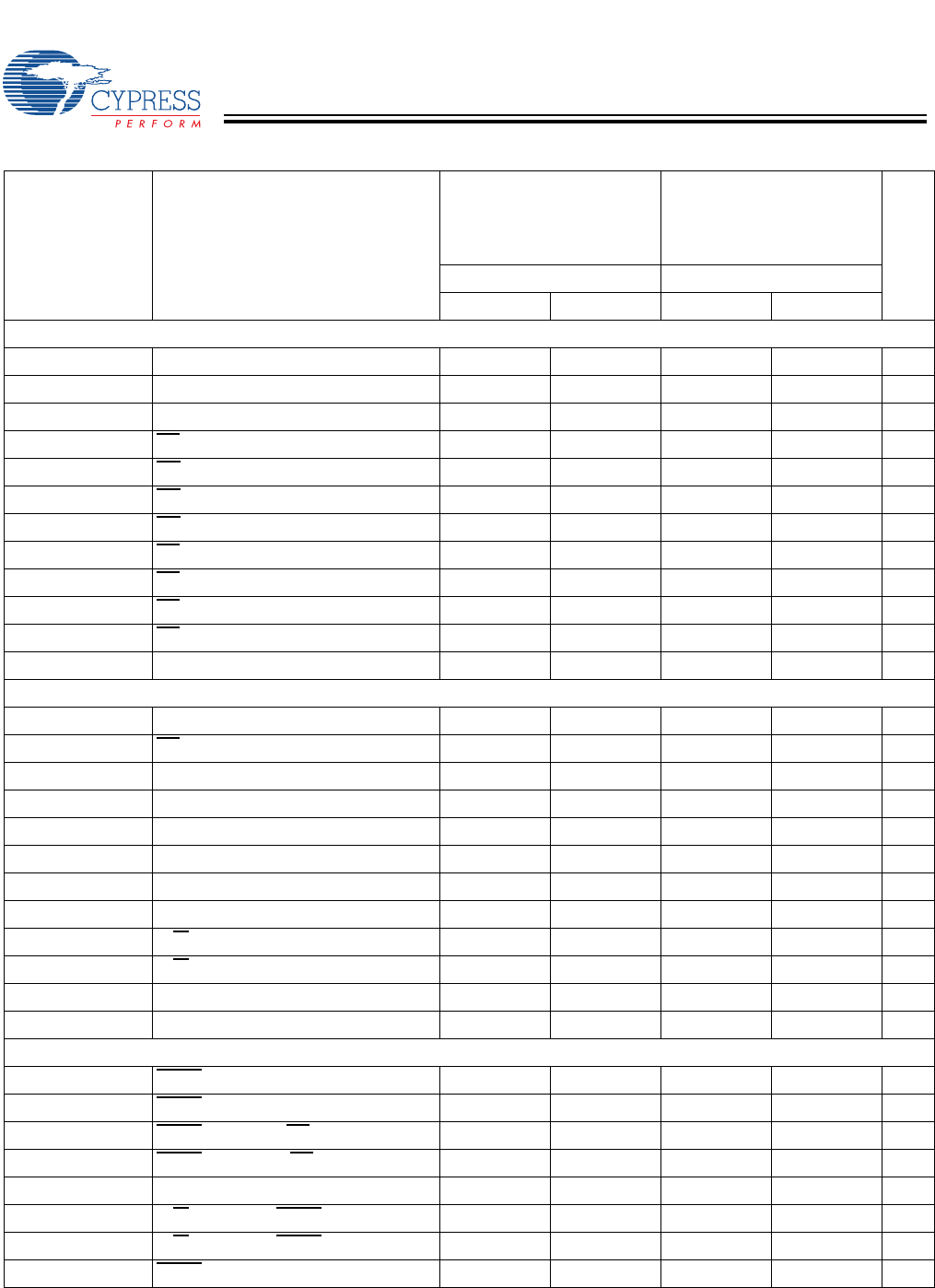

Switching Characteristics for V

CC

= 2.5V Over the Operating Range

Parameter Description

CYDC256B16,

CYDC128B16,

CYDC064B16,

CYDC128B08,

CYDC064B08

CYDC256B16,

CYDC128B16,

CYDC064B16,

CYDC128B08,

CYDC064B08

Unit

-40 -55

Min. Max. Min. Max.

Read Cycle

t

RC

Read Cycle Time 40 55 ns

t

AA

Address to Data Valid 40 55 ns

t

OHA

Output Hold From Address Change 5 5 ns

t

ACE

[28]

CE LOW to Data Valid 40 55 ns

t

DOE

OE LOW to Data Valid 25 30 ns

t

LZOE

[29, 30, 31]

OE Low to Low Z 2 2 ns

t

HZOE

[29, 30, 31]

OE HIGH to High Z 15 15 ns

t

LZCE

[29, 30, 31]

CE LOW to Low Z 2 2 ns

t

HZCE

[29, 30, 31]

CE HIGH to High Z 15 15 ns

t

PU

[31]

CE LOW to Power-Up 0 0 ns

t

PD

[31]

CE HIGH to Power-Down 40 55 ns

t

ABE

[28]

Byte Enable Access Time 40 55 ns

Write Cycle

t

WC

Write Cycle Time 40 55 ns

t

SCE

[28]

CE LOW to Write End 30 45 ns

t

AW

Address Valid to Write End 30 45 ns

t

HA

Address Hold From Write End 0 0 ns

t

SA

[28]

Address Set-up to Write Start 0 0 ns

t

PWE

Write Pulse Width 25 40 ns

t

SD

Data Set-up to Write End 20 30 ns

t

HD

Data Hold From Write End 0 0 ns

t

HZWE

[30, 31]

R/W LOW to High Z 15 25 ns

t

LZWE

[30, 31]

R/W HIGH to Low Z 0 0 ns

t

WDD

[32]

Write Pulse to Data Delay 55 80 ns

t

DDD

[32]

Write Data Valid to Read Data Valid 55 80 ns

Busy Timing

[33]

t

BLA

BUSY LOW from Address Match 30 45 ns

t

BHA

BUSY HIGH from Address Mismatch 30 45 ns

t

BLC

BUSY LOW from CE LOW 30 45 ns

t

BHC

BUSY HIGH from CE HIGH 30 45 ns

t

PS

[34]

Port Set-up for Priority 5 5 ns

t

WB

R/W HIGH after BUSY (Slave) 0 0 ns

t

WH

R/W HIGH after BUSY HIGH (Slave) 20 35 ns

t

BDD

[35]

BUSY HIGH to Data Valid 30 40 ns

[+] Feedback