16

1616

16

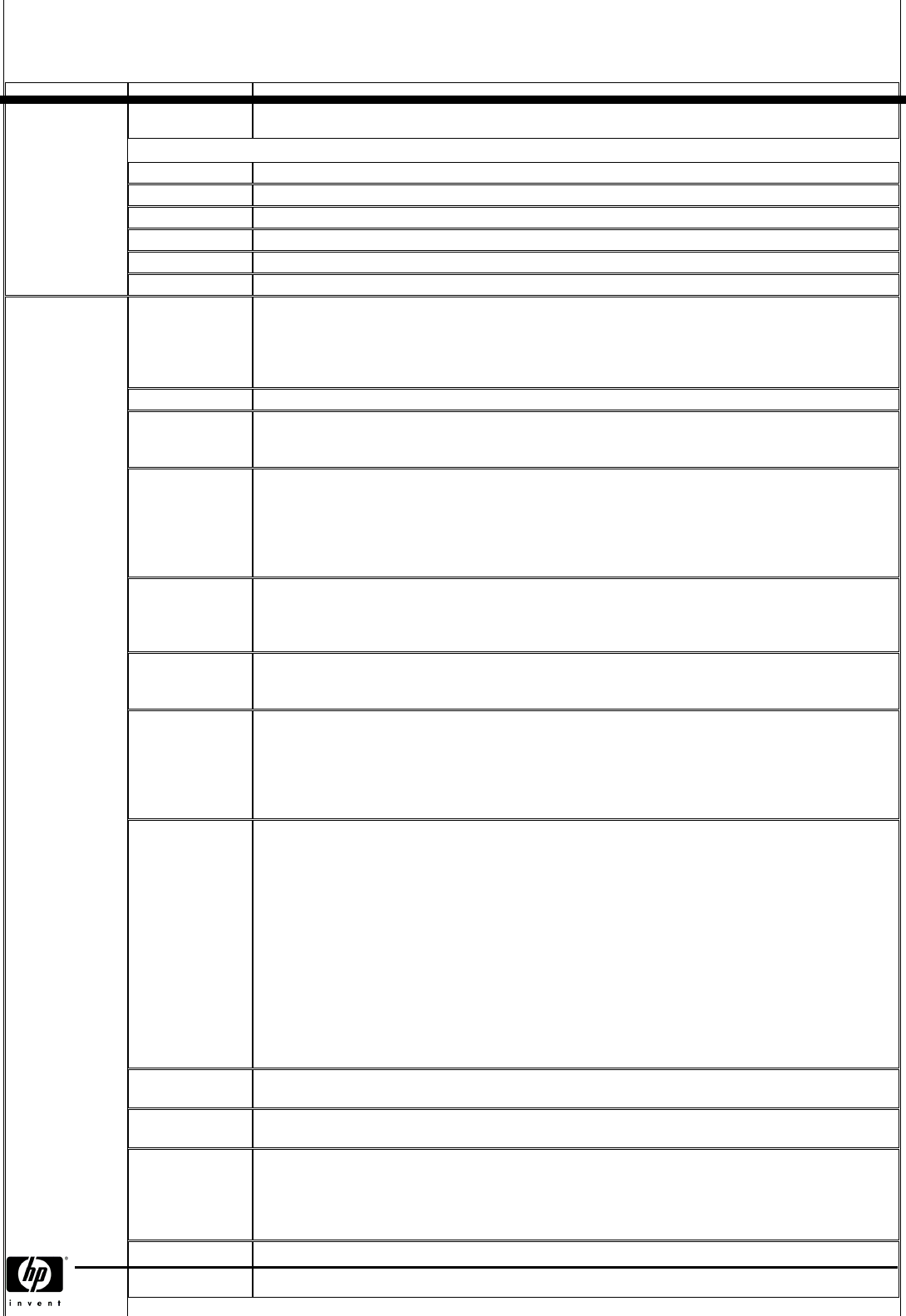

Removable media device controller should be in slot 8 of the I/O chassis.

Removable media device controller should be in slot 8 of the I/O chassis.Removable media device controller should be in slot 8 of the I/O chassis.

Removable media device controller should be in slot 8 of the I/O chassis.

17

1717

17

Core I/O card must be in slot 0 of the I/O chassis.

Core I/O card must be in slot 0 of the I/O chassis.Core I/O card must be in slot 0 of the I/O chassis.

Core I/O card must be in slot 0 of the I/O chassis.

18

1818

18

Boot device controller should be in slot 1 of the I/O chassis

Boot device controller should be in slot 1 of the I/O chassisBoot device controller should be in slot 1 of the I/O chassis

Boot device controller should be in slot 1 of the I/O chassis

19

1919

19

PCI-X high bandwidth I/O cards should be in the high bandwidth slots in the I/O chassis

PCI-X high bandwidth I/O cards should be in the high bandwidth slots in the I/O chassisPCI-X high bandwidth I/O cards should be in the high bandwidth slots in the I/O chassis

PCI-X high bandwidth I/O cards should be in the high bandwidth slots in the I/O chassis

20

2020

20

Every I/O card in an I/O chassis must be assigned to a valid physical location.

Every I/O card in an I/O chassis must be assigned to a valid physical location.Every I/O card in an I/O chassis must be assigned to a valid physical location.

Every I/O card in an I/O chassis must be assigned to a valid physical location.

21

2121

21

Every I/O chassis in a Superdome complex must be assigned to a valid physical location

Every I/O chassis in a Superdome complex must be assigned to a valid physical locationEvery I/O chassis in a Superdome complex must be assigned to a valid physical location

Every I/O chassis in a Superdome complex must be assigned to a valid physical location

Performance

PerformancePerformance

Performance

22

2222

22

The amount of memory on a cell should be evenly divisible by 4 GB if using 512-MB DIMMs

The amount of memory on a cell should be evenly divisible by 4 GB if using 512-MB DIMMsThe amount of memory on a cell should be evenly divisible by 4 GB if using 512-MB DIMMs

The amount of memory on a cell should be evenly divisible by 4 GB if using 512-MB DIMMs

or 8 GB if using 1-GB DIMMs, i.e. 8, 16 or 32 DIMMs. The cell has four memory subsystems

or 8 GB if using 1-GB DIMMs, i.e. 8, 16 or 32 DIMMs. The cell has four memory subsystemsor 8 GB if using 1-GB DIMMs, i.e. 8, 16 or 32 DIMMs. The cell has four memory subsystems

or 8 GB if using 1-GB DIMMs, i.e. 8, 16 or 32 DIMMs. The cell has four memory subsystems

and each subsystem should have an echelon (2 DIMMs) populated. The loading order of the

and each subsystem should have an echelon (2 DIMMs) populated. The loading order of theand each subsystem should have an echelon (2 DIMMs) populated. The loading order of the

and each subsystem should have an echelon (2 DIMMs) populated. The loading order of the

DIMMs alternates among the four subsystems. This rule provides maximum memory

DIMMs alternates among the four subsystems. This rule provides maximum memoryDIMMs alternates among the four subsystems. This rule provides maximum memory

DIMMs alternates among the four subsystems. This rule provides maximum memory

bandwidth on the cell, by equally populating all four memory subsystems.

bandwidth on the cell, by equally populating all four memory subsystems.bandwidth on the cell, by equally populating all four memory subsystems.

bandwidth on the cell, by equally populating all four memory subsystems.

23

2323

23

All cells in a partition should have the same number of processors.

All cells in a partition should have the same number of processors.All cells in a partition should have the same number of processors.

All cells in a partition should have the same number of processors.

24

2424

24

The number of active CPUs per cell should be balanced across the partition, however minor

The number of active CPUs per cell should be balanced across the partition, however minorThe number of active CPUs per cell should be balanced across the partition, however minor

The number of active CPUs per cell should be balanced across the partition, however minor

differences are OK. (Example: 4 active CPUs on one cell and three active CPUs on the

differences are OK. (Example: 4 active CPUs on one cell and three active CPUs on thedifferences are OK. (Example: 4 active CPUs on one cell and three active CPUs on the

differences are OK. (Example: 4 active CPUs on one cell and three active CPUs on the

second cell)

second cell)second cell)

second cell)

25

2525

25

If memory is going to be configured as fully interleaved, all cells in a partition should have

If memory is going to be configured as fully interleaved, all cells in a partition should haveIf memory is going to be configured as fully interleaved, all cells in a partition should have

If memory is going to be configured as fully interleaved, all cells in a partition should have

the same amount of memory (symmetric memory loading). Asymmetrically distributed memory

the same amount of memory (symmetric memory loading). Asymmetrically distributed memorythe same amount of memory (symmetric memory loading). Asymmetrically distributed memory

the same amount of memory (symmetric memory loading). Asymmetrically distributed memory

affects the interleaving of cache lines across the cells. Asymmetrically distributed memory

affects the interleaving of cache lines across the cells. Asymmetrically distributed memoryaffects the interleaving of cache lines across the cells. Asymmetrically distributed memory

affects the interleaving of cache lines across the cells. Asymmetrically distributed memory

can create memory regions that are non optimally interleaved. Applications whose memory

can create memory regions that are non optimally interleaved. Applications whose memorycan create memory regions that are non optimally interleaved. Applications whose memory

can create memory regions that are non optimally interleaved. Applications whose memory

pages land in memory interleaved across just one cell can see up to 16 times less bandwidth

pages land in memory interleaved across just one cell can see up to 16 times less bandwidthpages land in memory interleaved across just one cell can see up to 16 times less bandwidth

pages land in memory interleaved across just one cell can see up to 16 times less bandwidth

than ones whose pages are interleaved across all cells.

than ones whose pages are interleaved across all cells.than ones whose pages are interleaved across all cells.

than ones whose pages are interleaved across all cells.

26

2626

26

If a partition contains 4 or fewer cells, all the cells should be linked to the same crossbar

If a partition contains 4 or fewer cells, all the cells should be linked to the same crossbarIf a partition contains 4 or fewer cells, all the cells should be linked to the same crossbar

If a partition contains 4 or fewer cells, all the cells should be linked to the same crossbar

(quad) in order to eliminate bottlenecks and the sharing of crossbar bandwidth with other

(quad) in order to eliminate bottlenecks and the sharing of crossbar bandwidth with other(quad) in order to eliminate bottlenecks and the sharing of crossbar bandwidth with other

(quad) in order to eliminate bottlenecks and the sharing of crossbar bandwidth with other

partitions. In each Superdome cabinet, slots 0, 1, 2 and 3 link to the same crossbar and

partitions. In each Superdome cabinet, slots 0, 1, 2 and 3 link to the same crossbar andpartitions. In each Superdome cabinet, slots 0, 1, 2 and 3 link to the same crossbar and

partitions. In each Superdome cabinet, slots 0, 1, 2 and 3 link to the same crossbar and

slots 4, 5, 6 and 7 link to the same crossbar.

slots 4, 5, 6 and 7 link to the same crossbar.slots 4, 5, 6 and 7 link to the same crossbar.

slots 4, 5, 6 and 7 link to the same crossbar.

27

2727

27

A Core I/O card should not be selected as the main network interface to a partition. A Core

A Core I/O card should not be selected as the main network interface to a partition. A CoreA Core I/O card should not be selected as the main network interface to a partition. A Core

A Core I/O card should not be selected as the main network interface to a partition. A Core

I/O card is a PCI X 1X card that possibly produces lower performance than a comparable

I/O card is a PCI X 1X card that possibly produces lower performance than a comparableI/O card is a PCI X 1X card that possibly produces lower performance than a comparable

I/O card is a PCI X 1X card that possibly produces lower performance than a comparable

PCI X 2X card.

PCI X 2X card.PCI X 2X card.

PCI X 2X card.

28

2828

28

The number of cells in a partition should be a power of two, i.e., 2, 4, 8, or 16.

The number of cells in a partition should be a power of two, i.e., 2, 4, 8, or 16.The number of cells in a partition should be a power of two, i.e., 2, 4, 8, or 16.

The number of cells in a partition should be a power of two, i.e., 2, 4, 8, or 16.

Optimal interleaving of memory across cells requires that the number of cells be a power of

Optimal interleaving of memory across cells requires that the number of cells be a power ofOptimal interleaving of memory across cells requires that the number of cells be a power of

Optimal interleaving of memory across cells requires that the number of cells be a power of

two. Building a partition that does not meet this requirement can create memory regions that

two. Building a partition that does not meet this requirement can create memory regions thattwo. Building a partition that does not meet this requirement can create memory regions that

two. Building a partition that does not meet this requirement can create memory regions that

are non optimally interleaved. Applications whose memory pages land in the memory that is

are non optimally interleaved. Applications whose memory pages land in the memory that isare non optimally interleaved. Applications whose memory pages land in the memory that is

are non optimally interleaved. Applications whose memory pages land in the memory that is

interleaved across just one cell can experience up to 16 times less bandwidth than pages

interleaved across just one cell can experience up to 16 times less bandwidth than pagesinterleaved across just one cell can experience up to 16 times less bandwidth than pages

interleaved across just one cell can experience up to 16 times less bandwidth than pages

which are interleaved across all 16 cells.

which are interleaved across all 16 cells.which are interleaved across all 16 cells.

which are interleaved across all 16 cells.

29

2929

29

Before consolidating partitions in a Superdome 32-way or 64-way system, the following link

Before consolidating partitions in a Superdome 32-way or 64-way system, the following linkBefore consolidating partitions in a Superdome 32-way or 64-way system, the following link

Before consolidating partitions in a Superdome 32-way or 64-way system, the following link

load calculation should be performed for each link between crossbars in the proposed

load calculation should be performed for each link between crossbars in the proposedload calculation should be performed for each link between crossbars in the proposed

load calculation should be performed for each link between crossbars in the proposed

partition.

partition.partition.

partition.

Links loads less then 1 are best. As the link load begins to approach 2 performance

Links loads less then 1 are best. As the link load begins to approach 2 performanceLinks loads less then 1 are best. As the link load begins to approach 2 performance

Links loads less then 1 are best. As the link load begins to approach 2 performance

bottlenecks may occur.

bottlenecks may occur.bottlenecks may occur.

bottlenecks may occur.

For crossbars X and Y

For crossbars X and YFor crossbars X and Y

For crossbars X and Y

Link Load = Qx * Qy / Qt / L, where

Link Load = Qx * Qy / Qt / L, whereLink Load = Qx * Qy / Qt / L, where

Link Load = Qx * Qy / Qt / L, where

- Qx is the number of cells connected to crossbar X (quad)

- Qx is the number of cells connected to crossbar X (quad)- Qx is the number of cells connected to crossbar X (quad)

- Qx is the number of cells connected to crossbar X (quad)

- Qy is the number of cells connected to crossbar Y (quad)

- Qy is the number of cells connected to crossbar Y (quad)- Qy is the number of cells connected to crossbar Y (quad)

- Qy is the number of cells connected to crossbar Y (quad)

- Qt is the total number of cells in the partition

- Qt is the total number of cells in the partition- Qt is the total number of cells in the partition

- Qt is the total number of cells in the partition

- L is the number of links between crossbar X and Y (2 for Superdome 32-way systems and 1

- L is the number of links between crossbar X and Y (2 for Superdome 32-way systems and 1- L is the number of links between crossbar X and Y (2 for Superdome 32-way systems and 1

- L is the number of links between crossbar X and Y (2 for Superdome 32-way systems and 1

for Superdome 64-way systems)

for Superdome 64-way systems)for Superdome 64-way systems)

for Superdome 64-way systems)

30

3030

30

Maximum performance for optimal configurations (power of two cells, uniform memory

Maximum performance for optimal configurations (power of two cells, uniform memoryMaximum performance for optimal configurations (power of two cells, uniform memory

Maximum performance for optimal configurations (power of two cells, uniform memory

across cells, power of two DIMM ranks per cell)

across cells, power of two DIMM ranks per cell)across cells, power of two DIMM ranks per cell)

across cells, power of two DIMM ranks per cell)

31

3131

31

(If rule #30 cannot be met, rule #31 is recommended) Non-power of two cells, but still

(If rule #30 cannot be met, rule #31 is recommended) Non-power of two cells, but still(If rule #30 cannot be met, rule #31 is recommended) Non-power of two cells, but still

(If rule #30 cannot be met, rule #31 is recommended) Non-power of two cells, but still

uniform memory across cells, power of two DIMM ranks per cell, uniform type of DIMM.

uniform memory across cells, power of two DIMM ranks per cell, uniform type of DIMM.uniform memory across cells, power of two DIMM ranks per cell, uniform type of DIMM.

uniform memory across cells, power of two DIMM ranks per cell, uniform type of DIMM.

32

3232

32

(If rule #30 or #31 cannot be met, rule #32 is recommended) Same amount of memory in

(If rule #30 or #31 cannot be met, rule #32 is recommended) Same amount of memory in(If rule #30 or #31 cannot be met, rule #32 is recommended) Same amount of memory in

(If rule #30 or #31 cannot be met, rule #32 is recommended) Same amount of memory in

each cell, but possibly different memory types in each cell (for instance, a two cell

each cell, but possibly different memory types in each cell (for instance, a two celleach cell, but possibly different memory types in each cell (for instance, a two cell

each cell, but possibly different memory types in each cell (for instance, a two cell

configuration with 8 512MB DIMMs in one cell, and 4 1GB DIMMs in the other). Differences

configuration with 8 512MB DIMMs in one cell, and 4 1GB DIMMs in the other). Differencesconfiguration with 8 512MB DIMMs in one cell, and 4 1GB DIMMs in the other). Differences

configuration with 8 512MB DIMMs in one cell, and 4 1GB DIMMs in the other). Differences

in memory across different cells within the same partition should be minimal for the best

in memory across different cells within the same partition should be minimal for the bestin memory across different cells within the same partition should be minimal for the best

in memory across different cells within the same partition should be minimal for the best

performance.

performance.performance.

performance.

QuickSpecs

HP Integrity Superdome Servers: 16-way, 32-way,

HP Integrity Superdome Servers: 16-way, 32-way,HP Integrity Superdome Servers: 16-way, 32-way,

HP Integrity Superdome Servers: 16-way, 32-way,

and 64-way

and 64-wayand 64-way

and 64-way

Configuration

DA - 11717 Worldwide — Version 1 — June 30, 2003

Page 22