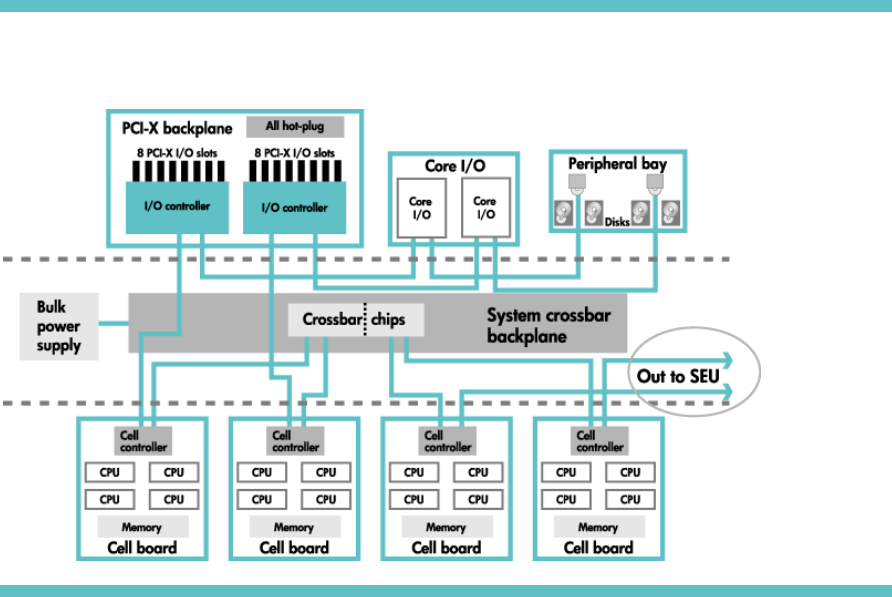

HP Integrity rx8620-32 Server architecture

The HP Integrity rx8620-32 Server architecture builds upon that of the Integrity rx7620-16 Server with

the addition of a crossbar backplane and two more cell boards. The crossbar backplane provides a

non-blocking connection between up to four cells, plus connection to the external I/O resources in the

HP Server Expansion Unit (SEU). Similarly to the Integrity rx7620-16 Server, the Integrity rx8620-32

Server can be configured as one 2- to 16-way (Intel Itanium 2 processor) or 2- to 32-way (HP mx2

Dual-Processor Module) SMP server, or it can be divided into smaller independent nPars. The Integrity

rx8620-32 Server can be divided into four hardware-isolated partitions when connected to the SEU.

Figure 7. Architecture of the HP Integrity rx8620-32 Server, showing the basic modular building blocks of the system and the

buses that connect them

HP Super-Scalable Processor Chipset sx1000

To support the growing needs in performance, scalability, and functionality, HP has developed the

new HP Super-Scalable Processor Chipset sx1000. The HP sx1000 Chipset consists of five distinct

ASICs: the cell controller, memory controller, system bus adapter, PCI-X host bridge adapter, and

crossbar. The HP sx1000 Chipset provides connectivity to Intel Itanium 2 processors, HP mx2 Dual-

Processor Modules, PA-8800 Processors, and future Intel Itanium and PA-RISC processors. In addition,

the HP sx1000 Chipset provides higher CPU and memory bandwidth, faster low-level error correction

than the previous chipset, and PCI-X support.

11