14 Specification Update

Identification Information

Component Identification using Programming Interface

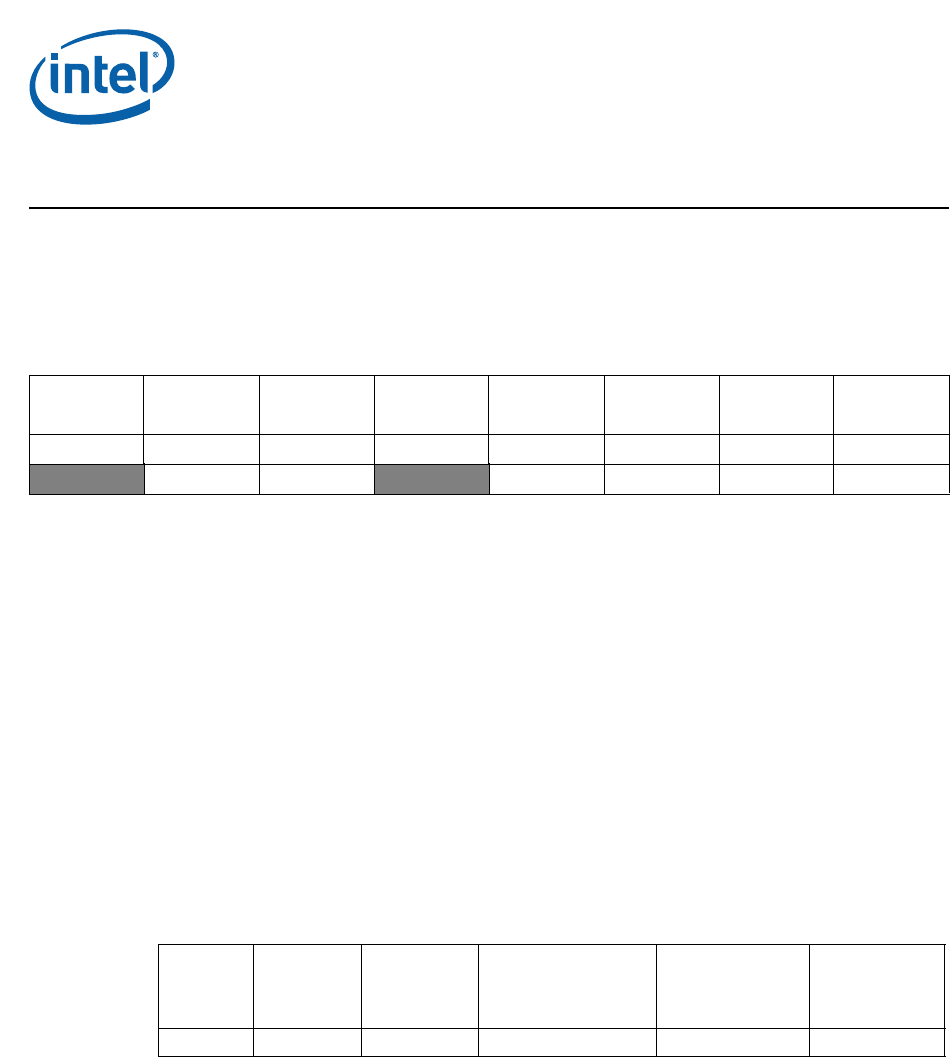

The processor stepping can be identified by the following register contents.

Notes:

1. The Extended Family, Bits [27:20] are used in conjunction with the Family Code, specified in Bits[11:8], to

indicate whether the processor belongs to the Intel386™, Intel486™, Pentium

®

, Pentium 4, or Intel

®

Core™ processor family.

2. The Extended Model, Bits [19:16] in conjunction with the Model Number, specified in Bits [7:4], are used to

identify the model of the processor within the processor’s family.

3. The Family Code corresponds to Bits [11:8] of the EDX register after RESET, Bits [11:8] of the EAX register

after the CPUID instruction is executed with a 1 in the EAX register, and the generation field of the Device

ID register accessible through Boundary Scan.

4. The Model Number corresponds to Bits [7:4] of the EDX register after RESET, Bits [7:4] of the EAX register

after the CPUID instruction is executed with a 1 in the EAX register, and the model field of the Device ID

register accessible through Boundary Scan.

5. The Stepping ID in Bits [3:0] indicates the revision number of that model. See the processor Identification

table for the processor stepping ID number in the CPUID information.

When EAX is initialized to a value of ‘1’, the CPUID instruction returns the Extended

Family, Extended Model, Processor Type, Family Code, Model Number and Stepping ID

value in the EAX register. Note that the EDX processor signature value after reset is

equivalent to the processor signature output value in the EAX register.

Cache and TLB descriptor parameters are provided in the EAX, EBX, ECX and EDX

registers after the CPUID instruction is executed with a 2 in the EAX register.

The processor can be identified by the following register contents.

Notes:

1. The Vendor ID corresponds to bits 15:0 of the Vendor ID Register located at offset 00h–01h in the PCI

function 0 configuration space.

2. The Host Device ID corresponds to bits 15:0 of the Device ID Register located at Device 0 offset 02h–

03h in the PCI function 0 configuration space.

3. The Processor Graphics Device ID (DID2) corresponds to bits 15:0 of the Device ID Register located at

Device 2 offset 02h–03h in the PCI function 0 configuration space.

4. The Revision Number corresponds to bits 7:0 of the Revision ID Register located at offset 08h in the PCI

function 0 configuration space.

Table 1. Desktop 4th Generation Intel

®

Core™ Processor Family Component

Identification

Reserved

Extended

Family

Extended

Model

Reserved

Processor

Type

Family

Code

Model

Number

Stepping

ID

31:28 27:20 19:16 15:14 13:12 11:8 7:4 3:0

00000000b 0011b 00b 0110b 1100b xxxxb

Stepping Vendor ID

1

Host Device

ID

2

Processor Graphics

Device ID

3

Revision ID

4

CRID

C-0 8086h 0C04h GT2 = 0416h 06h 06h