44 Evaluation Platform Board Manual

Intel

®

IQ80332 I/O Processor

Hardware Reference Section

3.9.6.8 Jumper J7B4: SMBus Header

3.9.6.9 Jumper J9D3: Buzzer Volume Control

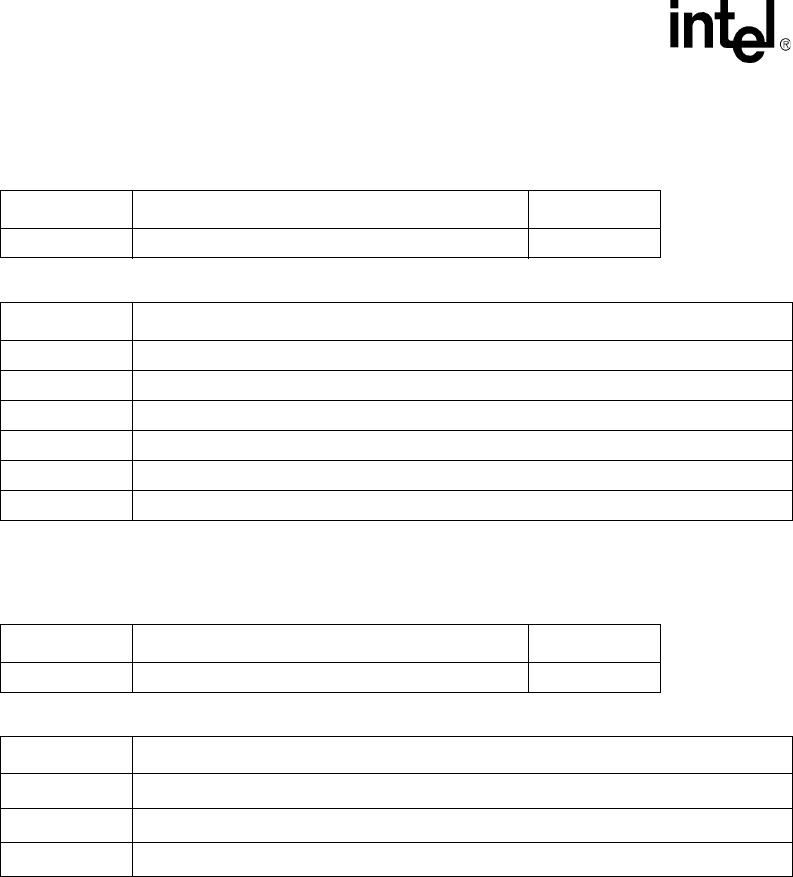

Table 37. Jumper J7B4: Descriptions

Jumper Description Factory Default

J7B4 SMBus Header 1-2, 3-4

Table 38. Jumper J7B4: Settings and Operation Mode

J7B4 Operation Mode

Pins 1, 2 Connects SM_SCLK to EEPROM U7B2 (Default Mode).

Pins 3, 4 Connects SM_SDTA to EEPROM U7B2 (Default Mode).

Pins 5, 6 Connects SM_SCLK to GE_SMCLK (for GBE control)

Pins 7, 8 Connects SM_SDTA to GE_SMDAT(for GBE control)r

Pins 9, 10 Connects SM_SCLK to PE_SMCLK (for PCI-E bus control)

Pins 11, 12 Connects SM_SDTA to PE_SM_SDAT (for PCI-E bus control)

Table 39. Jumper J9D3: Descriptions

Jumper Description Factory Default

J9D3 Buzzer Volume Open

Table 40. Jumper J9D3: Settings and Operation Mode

J9D3 Operation Mode

Pins 2, 3

Buzzer Volume Soft

Pins 1, 2

Buzzer Volume Loud.

NC

Buzzer Volume Off.