AT INTERFACE DESCRIPTION

5 – 5

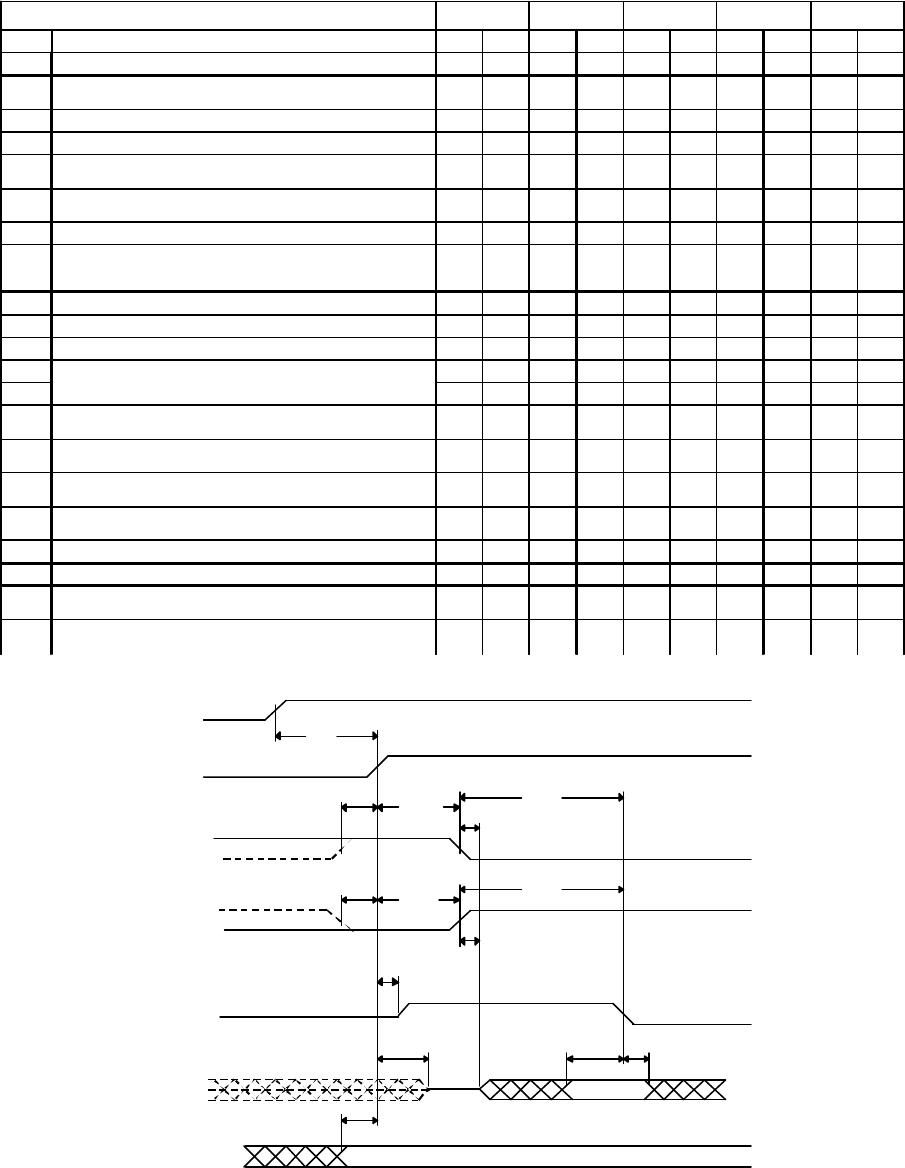

Ultra DMA Timing

TIMING PARAMETERS (all times in nanoseconds) MODE 0 MODE 1 MODE 2 MODE 3 MODE 4

MIN MAX MIN MAX MIN MAX MIN MAX MIN MAX

t

CYC

Cycle Time (from STROBE edge to STROBE edge) 112 73 54 39 25

t2

CYC

Two cycle time (from rising edge to next rising edge or

from falling edge to next falling edge of STROBE)

230 154 115 86 57

t

DS

Data setup time (at recipient) 15 10 7 7 5

t

DH

Data hold time (at recipient) 5 5 5 5 5

t

DVS

Data valid setup time at sender (time from data bus being

valid until STROBE edge)

70 48 30 20 6

t

DVH

Data valid hold time at sender (time from STROBE edge

until data may go invalid)

6 6 6 6 6

t

FS

First STROBE (time for device to send first STROBE) 0 230 0 200 0 170 0 130 0 120

t

LI

Limited interlock time (time allowed between an action by

one agent, either host or device, and the following action

by the other agent)

0 150 0 150 0 150 0 100 0 100

t

MLI

Interlock time with minimum 20 20 20 20 20

t

UI

Unlimited interlock time 0 0 0 0 0

t

AZ

Maximum time allowed for outputs to release 10 10 10 10 10

t

ZAH

Minimum delay time required for output drivers turning on

(from released state)

20 20 20 20 20

t

ZAD

0 0 0 0 0

t

ENV

Envelope time (all control signal transitions are within the

DMACK envelope by this much time)

20 70 20 70 20 70 20 55 20 55

t

SR

STROBE to DMARDY (response time to ensure the

synchronous pause case when the recipient is pausing)

50 30 20 NA NA

t

RFS

Ready-to-final-STROBE time (no more STROBE edges

may be sent this long after receiving DMARDY- negation)

75 70 60 60 60

t

RP

Ready-to-pause time (time until a recipient may assume

that the sender has paused after negation of DMARDY-)

160 125 100 100 100

t

IORDYZ

Pull-up time before allowing IORDY to be released 20 20 20 20 20

t

ZIORDY

Minimum time device shall wait before driving IORDY 0 0 0 0 0

t

ACK

Setup and hold times before assertion and negation of

DMACK-

20 20 20 20 20

t

SS

Time from STROBE edge to STOP assertion when the

sender is stopping

50 50 50 50 50

DMARQ

(device)

DMACK-

(host)

STOP

(host)

HDMARDY-

(host)

DSTROBE

(device)

DD(15:0)

t

ZAD

DA0, DA1, DA2,

CS0-, CS1-

t

UI

tZAD

t

ACK

tACK

t

ENV

tENV

t

ZIORDY

tFS

tFS

t

VDStAZ tDVH

tACK

Figure 5 - 4

Initiating an Ultra DMA Data In Burst