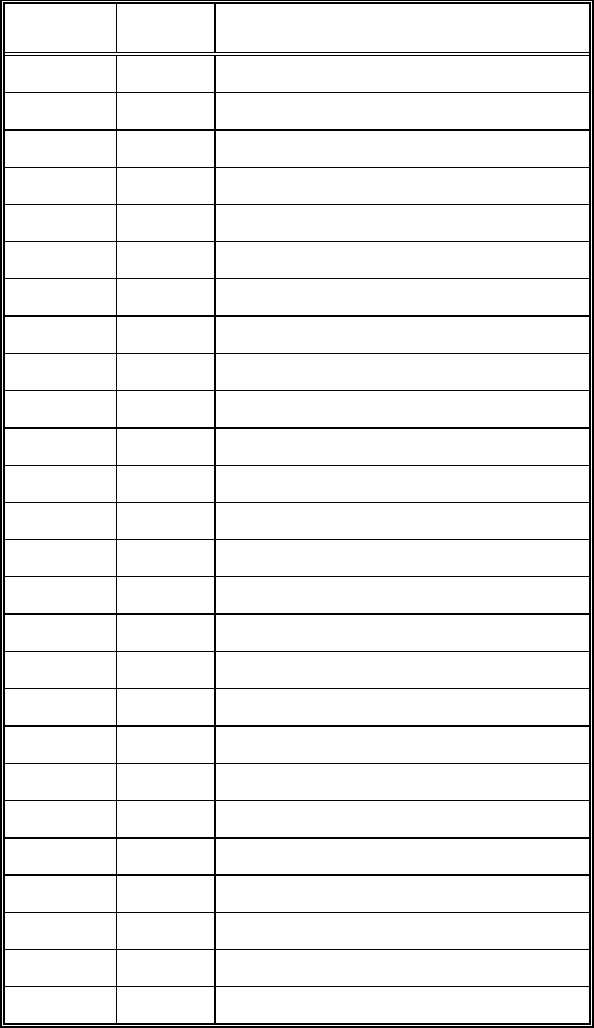

Beep code Contents

Port 80h

Description

None 01h CPU register test in progress.

1-1-3 02h CMOS read/write failure.

1-1-4 03h ROM BIOS check failure.

1-2-1 04h Programmable interval timer failure.

1-2-2 05h DMA initialization failure.

1-2-3 06h DMA page register write/read failure.

1-3-1 08h RAM refresh verification failure.

None 09h First 64K RAM test in progress.

1-3-3 0Ah First 64K RAM chip or data line failure (multi-bit).

1-3-4 0Bh First 64K RAM odd/even logic failure.

1-4-1 0Ch Address line failure first 64K RAM.

1-4-2 0Dh Parity failure first 64K RAM.

2-1-1 10h Bit 0 first 64K RAM failure.

2-1-2 11h Bit 1 first 64K RAM failure.

2-1-3 12h Bit 2 first 64K RAM failure.

2-1-4 13h Bit 3 first 64K RAM failure.

2-2-1 14h Bit 4 first 64K RAM failure.

2-2-2 15h Bit 5 first 64K RAM failure.

2-2-3 16h Bit 6 first 64K RAM failure.

2-2-4 17h Bit 7 first 64K RAM failure.

2-3-1 18h Bit 8 first 64K RAM failure.

2-3-2 19h Bit 9 first 64K RAM failure.

2-3-3 1Ah Bit 10 first 64K RAM failure.

2-2-4 1Bh Bit 11 first 64K RAM failure.

2-3-1 1Ch Bit 12 first 64K RAM failure.

2-4-2 1Dh Bit 13 first 64K RAM failure.

Micronics M5Pi System Board Manual

B-2