© National Instruments Corporation 7 NI PXI/PCI-5114 Specifications

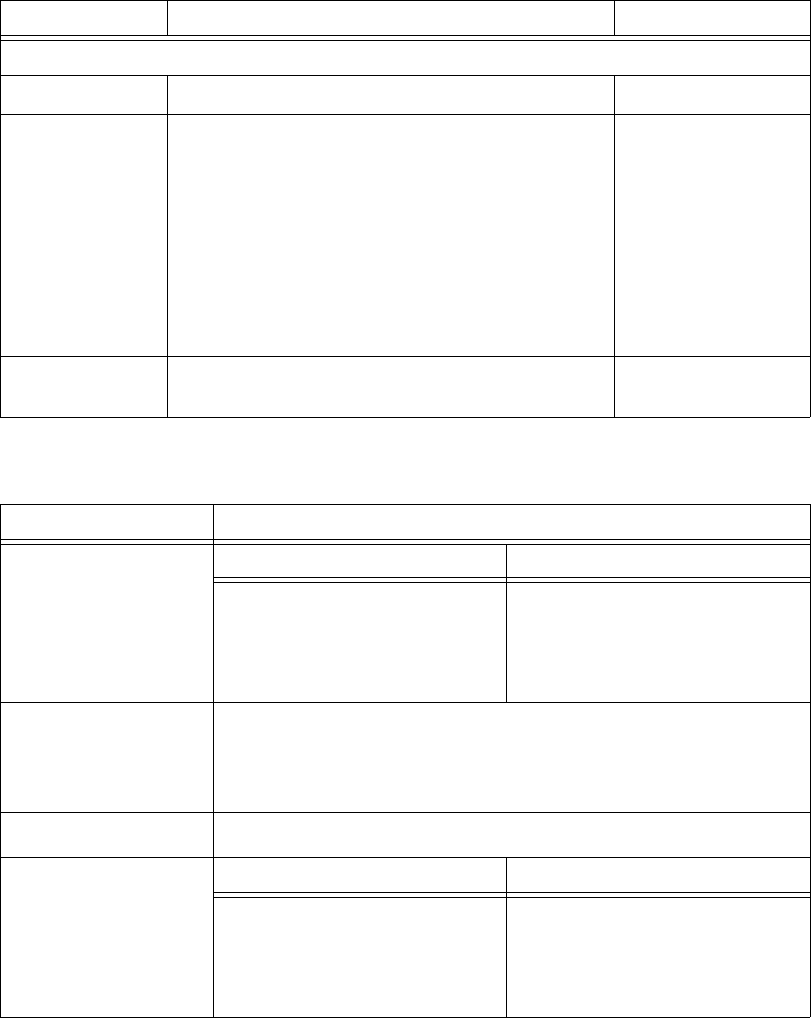

Phase-Locked Loop (PLL) Reference Clock

External Sample Clock

Sources CLK IN (front panel SMB connector) —

Frequency

Range

50 MHz to 250 MHz Divide by n

decimation

available where

1 ≤ n ≤ 65,535

For more information

about Sample Clock

and decimation, refer

to the NI High-Speed

Digitizers Help.

Duty Cycle

Tolerance

45% to 55% —

Specification Value

Sources NI PXI-5114 NI PCI-5114

PXI_CLK10

(backplane connector

)

CLK IN

(front panel SMB connector)

RTSI 7

CLK IN

(front panel SMB connector)

Frequency

Range

1 MHz to 20 MHz in 1 MHz increments

Default of 10 MHz

The PLL Reference Clock frequency must be accurate to ±50 ppm

Duty Cycle Tolerance 45% to 55%

Exported Reference

Clock Destinations

NI PXI-5114 NI PCI-5114

PFI <0..1> (front panel 9-pin

mini-circular DIN connector)

PXI_Trig <0..7> (backplane

connector)

PFI <0..1> (front panel 9-pin

mini-circular DIN connector)

RTSI <0..7>

Specification Value Comments