504

CHAPTER 21 INTERRUPT AND TEST FUNCTIONS

Main Processing

EI

INTxx

(PR=1)

INTyy

(PR=0)

IE=0

EI

RETI

INTxx

Servicing

INTzz

(PR=0)

IE=0

EI

RETI

INTyy

Servicing

IE=0

RETI

INTzz

Servicing

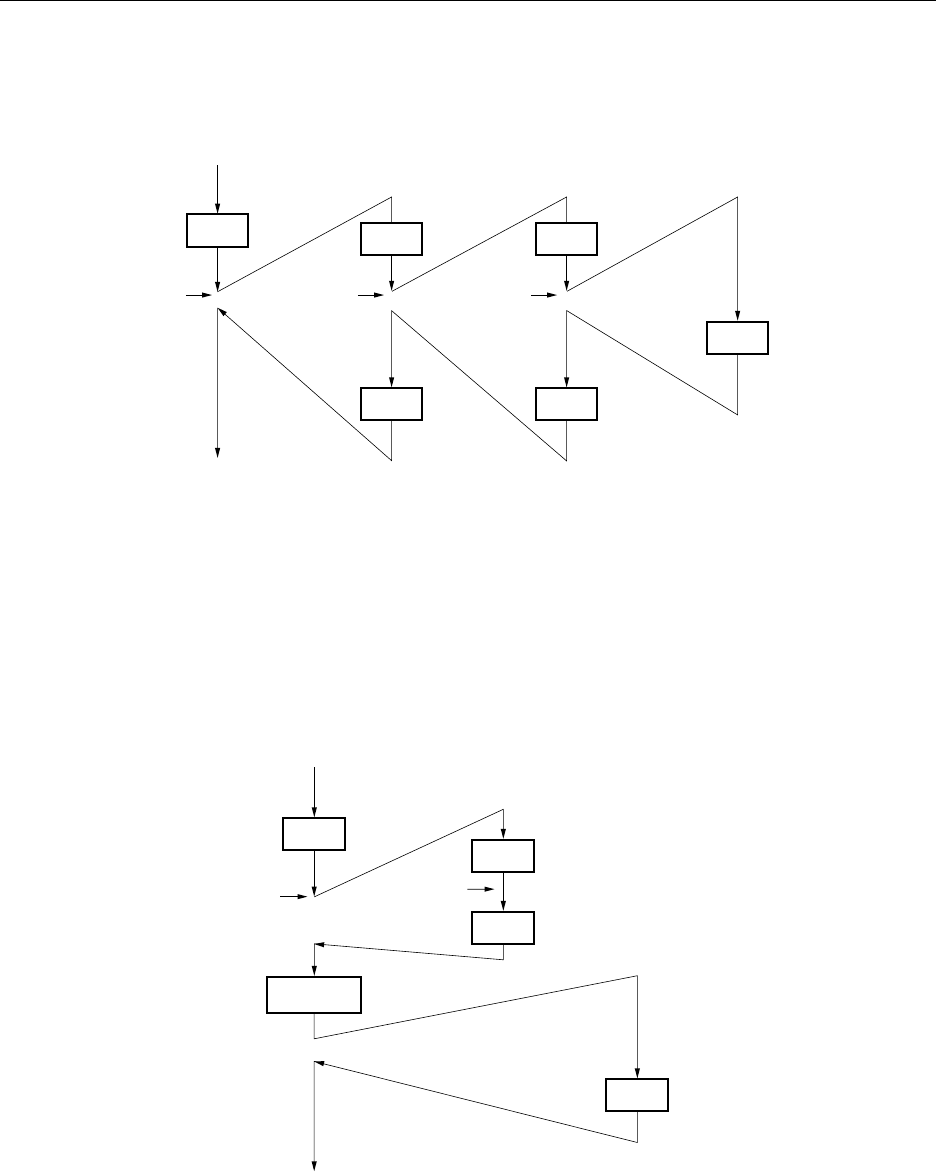

Figure 21-16. Multiple Interrupt Example (1/2)

Example 1. A multiple interrupt is generated at twice

While servicing interrupt INTxx, two interrupt requests, INTyy and INTzz, are acknowledged, and a multiple

interrupt is generated. Before each interrupt request acknowledgment, the EI instruction is always issued and

interrupt request acknowledgment is enabled.

PR = 0 : High priority level

PR = 1 : Low priority level

IE = 0 : Interrupt request acknowledgment disabled

Example 2. A multiple interrupt is not generated with priority control

Interrupt request INTyy generated while servicing interrupt INTxx is not acknowledged because it has a lower

priority than INTxx, and a multiple interrupt is not generated. The INTyy request is reserved and acknowledged after

execution of one main processing instruction.

PR = 0 : High priority level

PR = 1 : Low priority level

IE = 0 : Interrupt request acknowledgment disabled

Main Processing INTxx

Servicing

INTyy

Servicing

INTxx

(PR=0)

1 Instruction

Execution

IE=0

INTyy

(PR=1)

EI

IE=0

EI

RETI

RETI