245

CHAPTER 10 WATCH TIMER

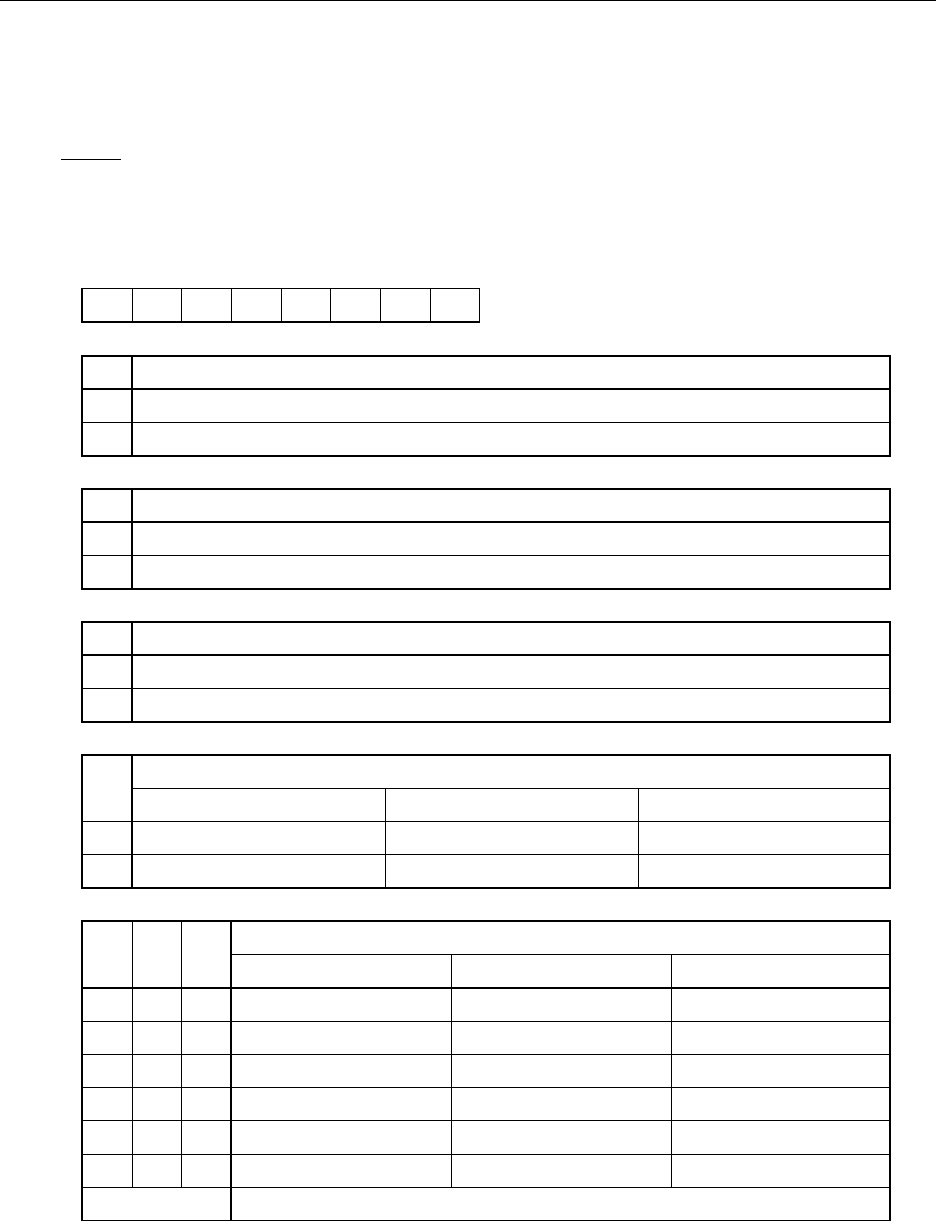

(2) Watch timer mode control register (TMC2)

This register sets the watch timer operating mode, watch flag set time and prescaler interval time and enables/

disables prescaler and 5-bit counter operations. TMC2 is set with a 1-bit or 8-bit memory manipulation

instruction.

RESET input sets TMC2 to 00H.

Figure 10-3. Watch Timer Mode Control Register Format

Caution When the watch timer is used, the prescaler should not be cleared frequently.

Remarks 1. f

W : Watch timer clock frequency (fXX/2

7

or fXT)

2. fXX : Main system clock frequency (fX or fX/2)

3. f

X : Main system clock oscillation frequency

4. fXT : Subsystem clock oscillation frequency

0

7

TMC26

6

TMC25 TMC24

4

TMC23

3210

FF4AH

Address

TMC2

Symbol

TMC22 TMC21 TMC20

5

00H

After

Reset

R/W

R/W

0

1

TMC23

fXX = 5.0 MHz Operation

2

14

/fW (0.4 sec)

2

13

/fW (0.2 sec)

Watch Flag Set Time Selection

0

0

0

0

1

1

Other than above

0

0

1

1

0

0

0

1

0

1

0

1

TMC26 TMC25 TMC24

fXX = 5.0 MHz Operation

2

4

/fW (410 s)

2

5

/fW (819 s)

2

6

/fW (1.64 ms)

2

7

/fW (3.28 ms)

2

8

/fW (6.55 ms)

2

9

/fW (13.1 ms)

Setting prohibited

f

XX = 4.19 MHz Operation

2

4

/fW (488 s)

2

5

/fW (977 s)

2

6

/fW (1.95 ms)

2

7

/fW (3.91 ms)

2

8

/fW (7.81 ms)

2

9

/fW (15.6 ms)

f

XT = 32.768 kHz Operation

2

4

/fW (488 s)

2

5

/fW (977 s)

2

6

/fW (1.95 ms)

2

7

/fW (3.91 ms)

2

8

/fW (7.81 ms)

2

9

/fW (15.6 ms)

Prescaler Interval Time Selection

µ

µ

µ

µ

µ

µ

fXX = 4.19 MHz Operation

2

14

/fW (0.5 sec)

2

13

/fW (0.25 sec)

f

XT = 32.768 kHz Operation

2

14

/fW (0.5 sec)

2

13

/fW (0.25 sec)

TMC22

0

1

5-Bit Counter Operation Control

Clear after operation stop

Operation enable

TMC21

0

1

Prescaler Operation Control

Clear after operation stop

Operation enable

TMC20

0

1

Watch Operating Mode Selection

Normal operating mode (flag set at f

W/2

14

)

Fast feed operating mode (flag set at f

W/2

5

)