7/30

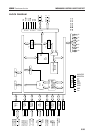

¡ Semiconductor MSM66201/66P201/66207/66P207

PIN DESCRIPTION

Type DescriptionSymbol

P0.0–P0.7/

AD0–AD7

P1.0–P1.7/

A8–A15

P2.0–P2.2

P2.5/HLDA

P2.6/T

X

C

AD: Outputs the lower 8 bits of program counter during external program memory fetch,

and receives the addressed instruction under the control of PSEN. This pin also

outputs the address and outputs or inputs data during an external data memory

access instruction, under the control of ALE, RD, and WR.

P1: 8-bit input-output port. Each bit can be assigned to input or output.

A: Outputs the upper 8 bits of program counter (PC

8–15

) during external program

memory fetch. This pin also outputs the upper 8 bits of address during external

data memory access instructions.

P2: 8-bit input-output port. Each bit can be assigned to input or output.

T

X

C: Transmitter clock input/output pin.

P3: 8-bit input-output port. Each bit can be assigned to input or output.

P2.4/HOLD

HOLD: Input pin to request the CPU to enter the hardware power-down state.

P3.0/T

X

D

P3.1/R

X

D

P0: 8-bit input-output port. Each bit can be assigned to input or output.

I/O

I/O

I/O

T

X

D: Transmitter data output pin.

I/O

HLDA: HOLD ACKNOWLEDGE: the HLDA signal appears in response to the HOLD

signal and indicates that the CPU has entered the power-down state.

P2.3/CLKOUT CLKOUT: Output pin for supplying a clock to peripheral circuits.

P2.7/R

X

CR

X

C: Receiver clock input/output pin.

P3.2/INT0 R

X

D: Receiver data input pin.

P3.3/INT1 INT: Interrupt request input pin.

Falling edge trigger or level trigger is selectable.

P3.4/TM0IO

TM0IO-TM3IO: One of the following signals is output or input.

P3.5/TM1IO

P3.6/TM2IO

P3.7/TM3IO

• Clock at twice the frequency range of the 16-bit timer overflow

• Load trigger signal to the capture register input

• Setting value output

Whether the signal is input or output depends on the mode.

P4.0/TM0CK P4: 8-bit input-output port. Each bit can be assigned to input or output.

P4.1/TM1CK TM0CK, TM1CK: Clock input pins of timer 0, timer 1.

P4.2/PWM0

P4.3/PWM1

P4.4

– P4.7/

TRANS0 –

TRANS3

TRANS: Transition detector.

The input pins which sense the falling edge and set the flag.

PWM: 16-bit pulse-width modulator output pin.

I/O

P5.0

– P5.7/

AI0 –AI7

P5: 8-bit input port.

AI: Analog signal input pin for A/D converter.

I