4.5.2 Clock Rate Multiplier

A standard serial port operates at a clock speed of 1.8432 MHz. In order

to achieve higher data rates, Quatech Enhanced Serial Adapters can operate at

two, four, or eight times this standard clock speed. This is controlled by the clock

rate multiplier bits in the Options Register.

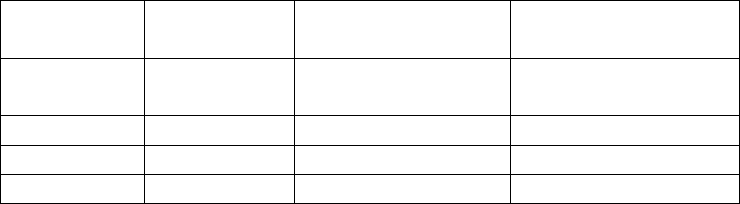

Software can determine the UART clock frequency by reading the clock

rate multiplier bits RR1 and RR0 in the Options Register as shown in Figure 12.

RR1 and RR0 can be set by writing to the Options Register if the X2 and X4

jumpers (J4-J5) are all removed. If one of these jumpers is applied, the RR1 and

RR0 bits are forced to the appropriate value. Reading the Options Register will

always return the clock rate multiplier at which the board is operating.

921.6 kbaud14.7456 MHzX811

460.8 kbaud 7.3728 MHzX401

230.4 kbaud3.6864 MHzX210

115.2 kbaud1.8432 MHz

X1

(default)

00

Maximum Data

Rate

UART Clock

Frequency

Clock Rate

Multiplier

RR0RR1

Figure 12 --- Rate Register bit definition

At powerup and reset, the Options Register is initialized to 0. The

DSCLP-200/300 will thus powerup in the x1 mode with software control of the

clock rate multiplier enabled as long as the X2 or X4 or X8 jumpers are not

installed.

Software can control high baud rates through a combination of changing

the clock rate multiplier and the UART baud rate divisor. For example, a baud

rate of 230.4 kbps could be achieved by setting the clock rate multiplier to X2

mode (or by applying the X2 jumper) and setting a software application for 115.2

kbps.

DSCLP/SSCLP-200/300 User's Manual 20