Spinpoint M8U-Internal Product Manual REV 3.4

41

INSTALLATION

6.2.2.2 Signaling

The signaling specification for the USB is described in the following subsections.

Overview of High-speed Signaling

A high-speed USB connection is made through a shielded, twisted pair cable that conforms to all current

USB cable specifications.

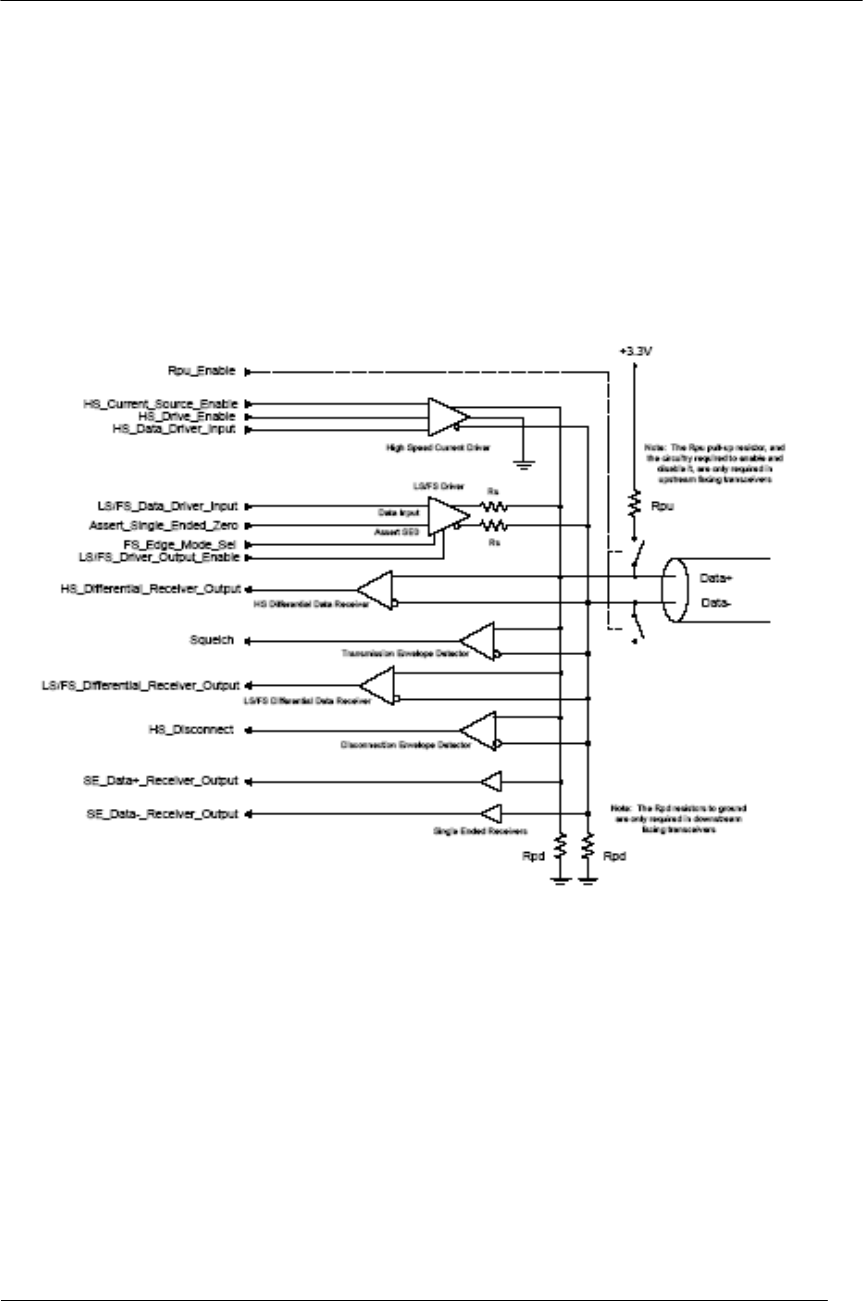

Figure 6-11 depicts an example implementation which largely utilizes USB 1.1 transceiver elements and adds

the new elements required for high-speed operation.

High-speed operation supports signaling at 480 Mb/s. To achieve reliable signaling at this rate, the cable is

terminated at each end with a resistance from each wire to ground. The value of this resistance (on each wire)

is nominally set to 1/2 the specified differential impedance of the cable, or 45Ω. This presents a differential

termination of 90Ω.

Figure 6-11: Example High-speed Capable Transceiver Circuit

For a link operating in high-speed mode, the high-speed idle state occurs when the transceivers at both ends of

the cable present high-speed terminations to ground, and when neither transceiver drives signaling current into

the D+ or D- lines. This state is achieved by using the low-/full-speed driver to assert a single ended zero, and

to closely control the combined total of the intrinsic driver output impedance and the R

S resistance (to 45

Ω,

nominal). The recommended practice is to make the intrinsic driver impedance as low as possible, and to let R

S

contribute as much of the 45Ω as possible. This will generally lead to the best termination accuracy

with the

least parasitic loading. In order to transmit in high-speed mode, a transceiver activates an internal current

source which is derived from its positive supply voltage and directs this current into one of the two data lines

via a high speed current steering switch. In this way, the transceiver generates the high-speed J or K state on

the cable.

The dynamic switching of this current into the D+ or D- line follows the same NRZI data encoding scheme

used in low-speed or full-speed operation and also in the bit stuffing behavior. To signal a J, the current is

directed into the D+ line, and to signal a K, the current is directed into the D- line. The SYNC field and the

EOP delimiters have been modified for high-speed mode.