ELECTRICAL SPECIFICATION SSD-HXXX(I)-3500 DATA SHEET

SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

3500H-03DSR PAGE 11 FEBRUARY 2, 2009

AC CHARACTERISTICS

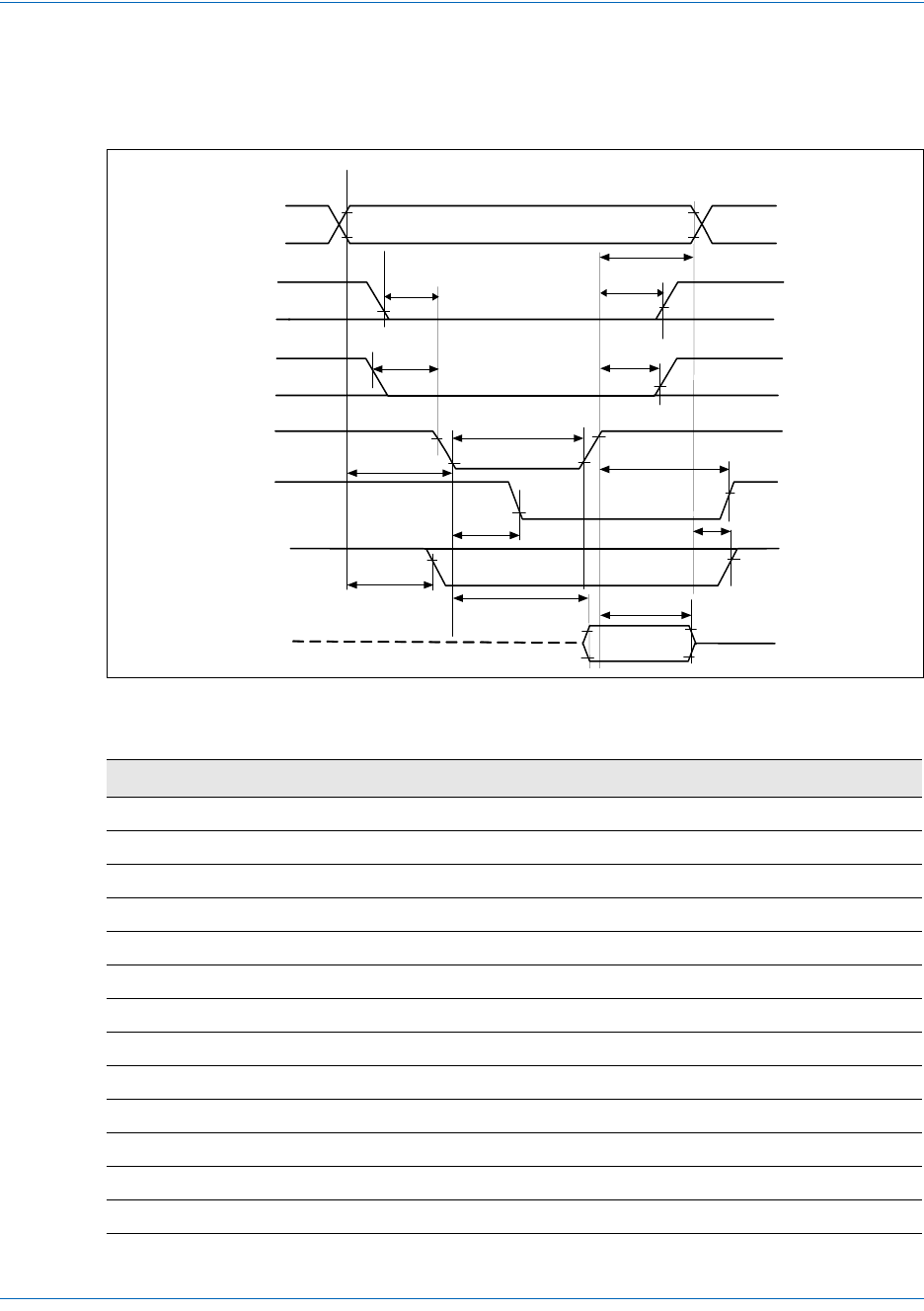

I/O Access Read Timing

Figure 4: I/O Access Read Timing Diagram

Note: (1) IOIS16 and INPACK are not supported.

Table 13: I/O Access Read Timing

Symbol Parameter Minimum Maximum Units

t

DVRL

Data Delay after IORD - 50 ns

t

IGHQX

Data Hold following IORD 5 - ns

t

IGLIGH

IORD Pulse Width 65 - ns

t

AVIGL

Address Setup before IORD 25 - ns

t

GHAX

Address Hold following IORD 10 - ns

t

CLIGL

CE Setup before IORD 5 - ns

t

CHIGH

CE Hold following IORD 10 - ns

t

RLIGL

REG Setup before IORD 5 - ns

t

RHIGH

REG Hold following IORD 0 - ns

t

IGLINL

INPACK Delay falling from IORD - (1) ns

t

IGHINH

INPACK Delay Rising from IORD - (1) ns

t

AVISL

IOIS16 Delay Falling from Address - (1) ns

t

AXISH

IOIS16 Delay Rising from Address - (1) ns

A[10::0]

____

REG

__

CE

___

IORD

______

INPACK

______

IOIS16

tRLIGL

tGHAX

D[15::0]

tCLIGL

tCHIGH

tRHIGH

tIGLIGH

tAVIGL

tIGHINH

tIGLINL

tAXISH

tAVISL

tDVRL

tIGHQX