High Performance

The Si5324 is the industry’s lowest jitter

genlock clock IC. The device provides any-

rate frequency synthesis simplifying HD

video and audio clock generation. With

jitter performance of 5 ps pk-pk, the Si5324

delivers significant jitter margin in 3G-SDI

serializer applications, reducing design risk

and improved link performance.

Highly Integrated

The Si5324 offers the industry’s most

highly integrated video clock generator IC

requiring no external PLL components (low

pass filter, charge pump, or VCXO). Because

all PLL components are integrated, board-

level noise immunity is improved reducing

design risk versus traditional video clock IC

solutions.

Any-Rate Frequency Flexibility

The Si5324’s any rate frequency flexibility

enables a single device to generate all

common genlock reference frequencies

required in next-generation SD/HD video

and audio equipment. The Si5324 is easily

reconfigurable via I2C/SPI interface and

requires no component changes for different

frequency plans, simplifying design reuse.

ANY-RATE FREQUENCY

FLEXIBILITY

www.silabs.com/Timing

Any-Rate Jitter Attenuating Clock Multipliers, Clock Generators and Buffers

DSPLL, Silicon Laboratories and the Silicon Labs logo are trademarks of Silicon Laboratories Inc.

All other product or service names are the property of

their respective owners. For the most up to date information please see your sales representative or visit our website at www.silabs.com.

100, August 09, Rev A SOL-VTS-2009A

Silicon Laboratories Inc.

400 West Cesar Chavez • Austin, TX 78701

Toll Free: (877) 444-3032

Email: ClockInfo@silabs.com or

VCXOInfo@silabs.com

Web site: www.silabs.com

Single and Multi-Frequency Crystal-Based XO/VCXO

2 WEEK

LEAD

TIMES

Built to Order Samples

Silicon Labs offers an easy-to-use web utility to build and confi gure the

right XO/VCXO for your application. Samples of any frequency XO/VCXO

are available in less than two weeks. www.silabs.com/BuyXO

Part

Number

Input/

Output

Clocks

Control Input Frequency Output Frequency Jitter

Minimum

PLL

Bandwidth

Jitter

Attenuation

Clock

Generation

Clock

Distribution

Package

Si5324 2/2 Diff I

2

C or SPI 2 kHz to 710 MHz 2 kHz to 1.4 GHz 5 ps pk-pk 4 Hz • • • 36-QFN

Si5368 4/5 Diff I

2

C or SPI 2 kHz to 710 MHz 2 kHz to 1.4 GHz 8 ps pk-pk 60 Hz • • • 100-TQFP

Si5338 4/4 Diff I

2

C or SPI

8 to 30 MHz (xtal)

160 kHz to 710 MHz (clock)

160 kHz to

710 MHz

36 ps pk-pk 1.6 MHz • • 24-QFN

Si5330

1:4 Diff

1:8 SE

Pin

5 to 710 MHz Diff

5 to 350 MHz SE

5 to 710 MHz Diff

5 to 350 MHz SE

55 fs rms

—

• 24-QFN

Part Number Type Frequency Control Frequency Range Jitter Stability/APR Options (ppm) Kv Options (ppm/V) Package

Si530/1 XO Single Pin

10 to 945 MHz

970 to 1134 MHz

1213 to 1417 MHz

0.3 ps rms

±20

±31.5

±61.5

N/A 6-pad

Si532/3 XO Dual Pin N/A 6-pad

Si534 XO Quad Pin N/A 8-pad

Si550 VCXO Single Pin

10 to 945 MHz

970 to 1134 MHz

1213 to 1417 MHz

0.5 ps rms ±12 to ±375 33 to 356

6-pad

Si552 VCXO Dual Pin 6-pad

Si554 VCXO Quad Pin 8-pad

Si570 XO Programmable Any-Rate I

2

C

10 to 280 MHz

10 to 810 MHz

10 to 1417 MHz

0.3 ps rms ±31.5; ±61.5 N/A 8-pad

Si571 VCXO Programmable Any-Rate I

2

C 0.5 ps rms ±12 to ±375 33 to 356 8-pad

Si590/1 XO Single Pin

10 to 525 MHz

0.7 ps rms ±30; ±50; ±100 N/A 6-pad

Si595 VCXO Single Pin 0.7 ps rms ±10 to ±370 45 to 380 6-pad

Video Timing Solutions

Recommended Silicon Labs Timing Solutions for Video

Si534 XO/Si554 VCXO

• Eliminates multiple oscillators,

reduces system cost

• Simplifies BOM and saves board

space and inventory

• Ideal for multi-rate FPGA-based PLLs

Industry’s Only Quad and Any-Rate Frequency XO/VCXOs

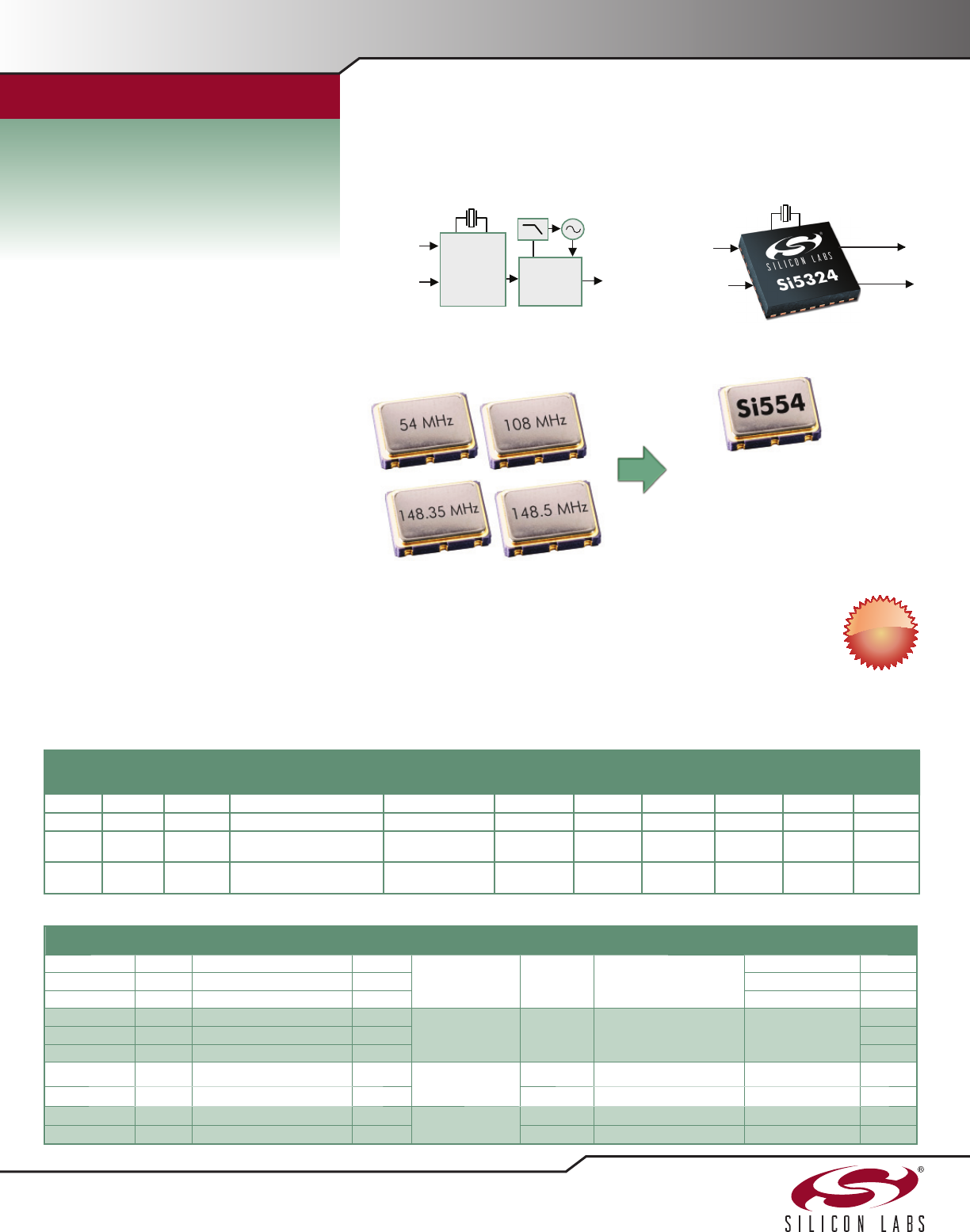

3G-SDI

Clock

Jitter

Cleaner

VCXO

Loop

Filter

Video

PLL with

Genlock

Crystal

HSYNC

SDI

Reference

Traditional Video Clock Solution Silicon Labs Solution

HSYNC

SDI

Reference

3G-SDI

Clock

SD

Clock

Crystal

vs.

Industry’s Most Integrated Genlock Solution

Silicon Labs’ Si5324 replaces multi-component video clock ICs, external loop fi lter and

VCXO components with a single IC, simplifying genlock designs.