Desktop System Controller Hub with Advanced, 8051µC-Based Auto Fan Control

Revision 0.6 (01-09-08) 4 SMSC SCH5617

PRODUCT PREVIEW

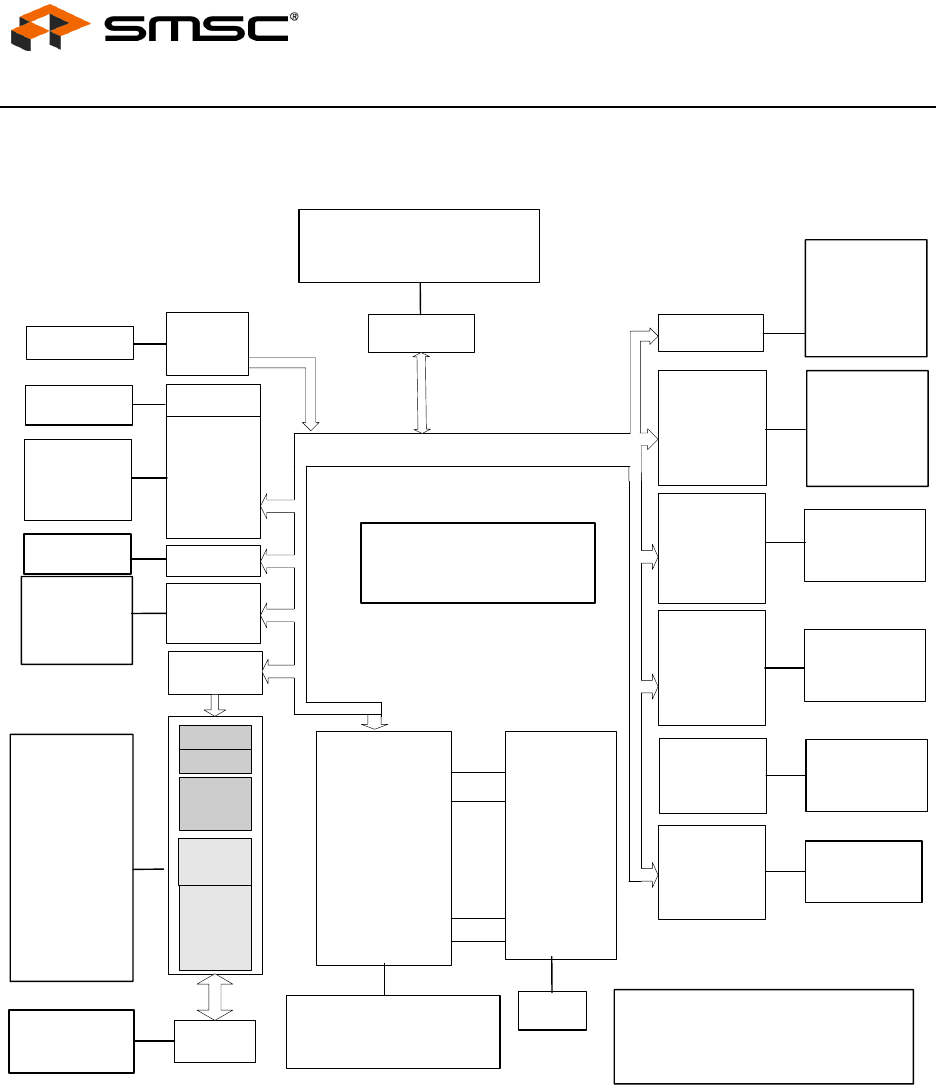

Block Diagram

Figure 1 SCH5617 Block Diagram

SCH5617

(128 QFP)

DIGITAL DATA

SEPARATOR

WITH WRITE

PRECOM-

PENSATION

SMC PROPRIETARY

82077 COMPATIBLE

VERTICAL

FLOPPYDISK

CONTROLLER CORE

WDATA

WCLOCK

RCLOCK

RDATA

Multi-Mode

Parallel Port

with ChiProtect

TM

LEDs

Internal Bus

(Data, Address, and Control lines)

High-Speed

16550A

UART

PORT 1

Keyboard/Mouse

8042

controller

High-Speed

16550A

UART

PORT 2

Power Mgmt

General

Purpose

I/O

Note 1: This diagram does not show power and ground

connections.

Note 2: Functions with "*" are located on multifunctional

pins. This diagram is designed to show the various

functions available on the chip (not pin layout).

CLOCK

GEN

LPC

Bus Interface

SERIAL

IRQ

Glue Logic

TACH1

TACH2

TACH3

HVSS

Remote1+

Remote1-

Remote2+

Remote2-

HVTR

PWM1

PWM2

PWM3

PROCHOT_IN#

PROCHOT_OUT

IDE_RSTDRV#*, PCI_RST_SYS#*

PCI_RST_SLOTS#*, PS_ON#*

PWR_GOOD_3V*, PWRGD_PS, RSMRST#*

SECONDARY_HD#*

PRIMARY_HD#*

SCSI#*

HD_LED#*

LED2*

LED3*

LED1*

LAD[3:0]

LFRAME#

LDRQ#

PCI_RESET#

LPCPD#

SER_IRQ

PCI_CLK

IO_PME#*

IO_SMI#*

PD[7:0]

BUSY,SLCT,PE

ERROR#, ACK#

STROBE#, INIT#

SLCTIN#

ALF#

TXD1*,RXD1*

CTS1#*, RTS1#*

DSR1#*, DTR1#*

DCD1#*, RI1#*

TXD2*,RXD2*

CTS2#*, RTS2#*

DSR2#*, DTR2#*

DCD2#*, RI2#*

KCLK, MCLK

KDAT, MDAT,

KBDRST#, A20M

P12*,P16*,P17*

RDATA#,

WDATA#

MRT0#, MRT1#*, TRK0#,

INDEX#,WRTPRT#,WGATE#,

HDSEL#,DRVDEN0*,

DIR#, STEP#, DSKCHG#,DS0#, DS1#*

8051

Analog

Interface

Analog

Block

Auto

Fan

Control

ROM

14.318 MHz

PECI

Interface

SMBus Isolation

Circuits

SCLK*, SDAT*

SCLK_1*, SDAT_1*

PECI V

REF

PECI IO

PECI READY

GP10*, GP11*, GP15*, GP21*,

GP22*, GP23*, GP25*, GP26*,

GP31*, GP33*, GP35*, GP36*,

GP37*, GP40*, GP41*, GP42*,

GP52*, GP53*, GP55*, GP57*,

GO60*, GP61*, GP75*, GP76*,

GP77*, GP80*, GP81*, GP82,

GP83*, GP84*, GP8051_[12:1]*,

GP8051_[17:14]*

Runtime

Registers