TMP92CZ26A

92CZ26A-254

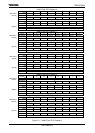

The NAND Flash ECC register is used to read ECC generated by the ECC generator.

After valid data has been written to or read from the NAND Flash, setting

NDFMCR0<ECCE> to “0” causes the corresponding ECC to be set in this register. (The

ECC in this register is updated when NDFMCR0<ECCE> changes from “1” to “0”.)

When Hamming codes are used, 22 bits of ECC are generated for up to 256 bytes of valid

data. In the case of Reed-Solomon codes, 80 bits of ECC are generated for up to 518 bytes of

valid data. A total of 80 bits of registers are provided, arranged as five 16-bit registers.

These registers must be read in 16-bit units and cannot be accessed in 32-bit units.

After ECC calculation has completed, in the case of Hamming codes, the 16-bit line

parity for the first 256 bytes is stored in the NDECCRD0 register, the 6-bit column parity

for the first 256 bytes in the NDECCRD1 register (<ECCE7:2>), the 16-bit line parity for

the second 256 bytes in the NDECCRD2 register, and the 6-bit column parity for the second

256 bytes in the NDECCRD3 register (<ECCD7:2>). In this case, the NDECCRD4 register

is not used.

In the case of Reed-Solomon codes, 80 bits of ECC are stored in the NDECCRD0,

NDECCRD1, NDECCRD2, NDECCRD3 and NDECCRD4 registers.

Note: Before reading ECC from the NAND Flash ECC register, be sure to set NDFMCR0<ECCE> to “0”.

The ECC in the NAND Flash ECC register is updated when NDFMCR0<ECCE> changes from “1” to

“0”. Also note that when the ECC in the ECC generator is reset by NDFMCR0<ECCRST>, the

contents of this register are not reset.

Register Name Hamming Reed-Solomon

NDECCRD0 [15:0] Line parity

(for the first 256 bytes)

[15:0]

Reed-Solomon ECC code 79:64

NDECCRD1 [7:2] Column parity

(for the first 256 bytes)

[15:0]

Reed-Solomon ECC code 63:48

NDECCRD2 [15:0] Line parity

(for the second 256 bytes)

[15:0]

Reed-Solomon ECC code 47:32

NDECCRD3 [7:2] Column parity

(for the second 256 bytes)

[15:0]

Reed-Solomon ECC code 31:16

NDECCRD4 Not in use [15:0]

Reed-Solomon ECC code 15:0

The table below shows an example of how ECC is written to the redundant area in the

NAND Flash memory when using Reed-Solomon codes.

When using Hamming codes with SmartMedia™, the addresses of the redundant area

are specified by the physical format of SmartMedia™. For details, refer to the

SmartMedia™ Physical Format Specifications.

Register Name Reed-Solomon NAND Flash Address

NDECCRD0 [15:0]

Reed-Solomon ECC code 79:64

Upper 8 bits [79:72]→ address 518

Lower 8 bits [71:64]

→ address 519

NDECCRD1 [15:0]

Reed-Solomon ECC code 63:48

Upper 8 bits [63:56] → address 520

Upper 8 bits [55:48]

→ address 521

NDECCRD2 [15:0]

Reed-Solomon ECC code 47:32

Upper 8 bits [47:40] → address 522

Lower 8 bits [39:32]

→ address 523

NDECCRD3 [15:0]

Reed-Solomon ECC code 31:16

Upper 8 bits [31:24] → address 524

Lower 8 bits [23:16]

→ address 525

NDECCRD4 [15:0]

Reed-Solomon ECC code 15:0

Upper 8 bits [15:8] → address 526

Lower 8 bits [7:0]

→ address 527