T

T

T

S

S

S

8

8

8

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

-

-

-

S

S

S

T

T

T

S

S

S

1

1

1

6

6

6

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

-

-

-

S

S

S

T

T

T

S

S

S

3

3

3

2

2

2

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

-

-

-

S

S

S

/

/

/

M

M

M

T

T

T

S

S

S

6

6

6

4

4

4

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

-

-

-

S

S

S

/

/

/

M

M

M

T

T

T

S

S

S

1

1

1

2

2

2

8

8

8

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

-

-

-

M

M

M

2.5” Solid State Disk

Transcend Information Inc.

V1.09

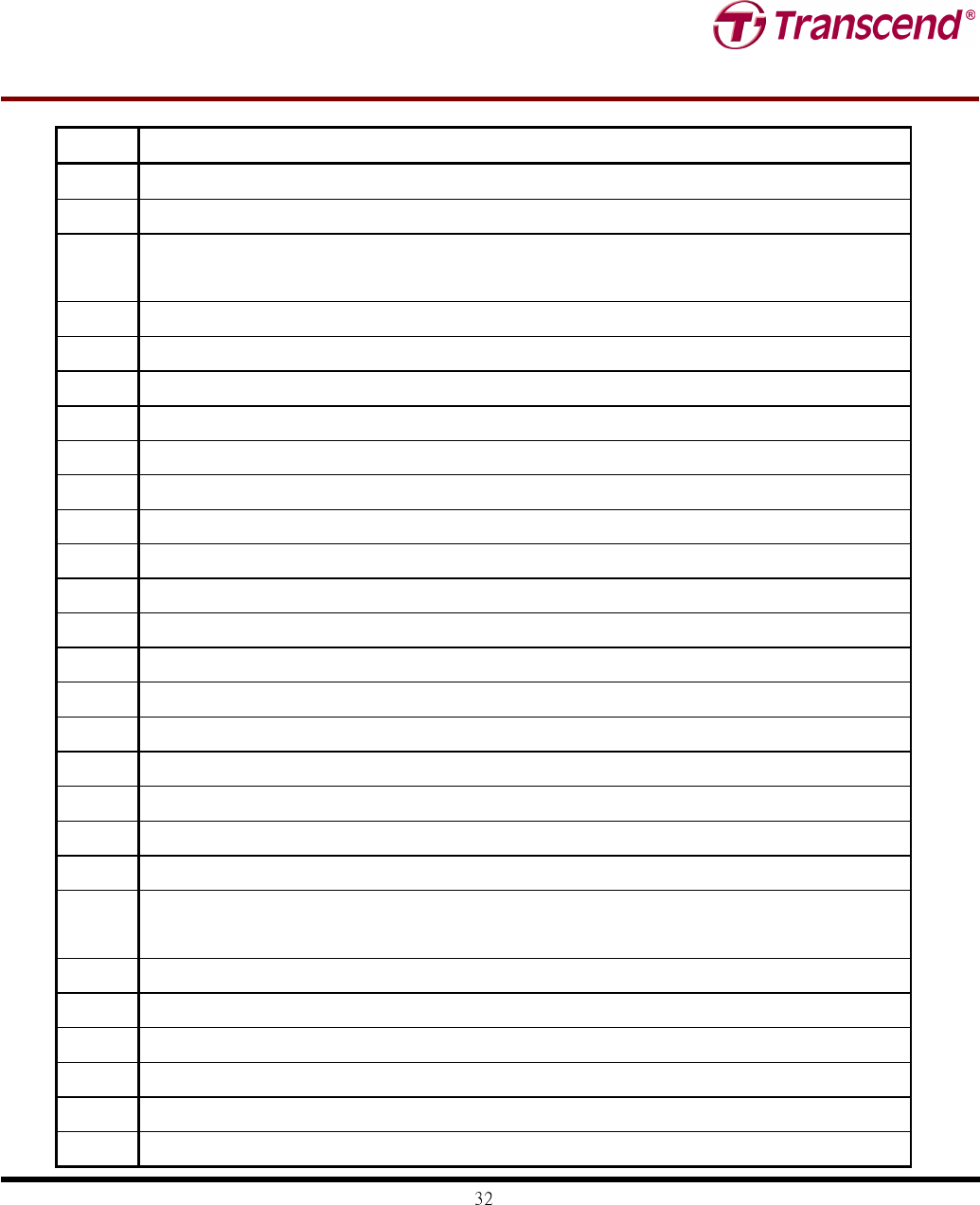

Ultra DMA data burst timing descriptions

Name Comment

t

2CYCTYP

Typical sustained average two cycle time

t

CYC

Cycle time allowing for asymmetry and clock variations (from STROBE edge to STROBE edge)

t

2CYC

Two cycle time allowing for clock variations (from rising edge to next rising edge or from falling edge to

next falling edge of STROBE)

t

DS

Data setup time at recipient (from data valid until STROBE edge)

t

DH

Data hold time at recipient (from STROBE edge until data may become invalid)

t

DVS

Data valid setup time at sender (from data valid until STROBE edge)

t

DVH

Data valid hold time at sender (from STROBE edge until data may become invalid)

t

CS

CRC word setup time at device

t

CH

CRC word hold time device

t

CVS

CRC word valid setup time at host (from CRC valid until DMACK- negation)

t

CVH

CRC word valid hold time at sender (from DMACK- negation until CRC may become invalid)

t

ZFS

Time from STROBE output released-to-driving until the first transition of critical timing.

t

DZFS

Time from data output released-to-driving until the first transition of critical timing.

t

FS

First STROBE time (for device to first negate DSTROBE from STOP during a data in burst)

t

LI

Limited interlock time

t

MLI

Interlock time with minimum

t

UI

Unlimited interlock time

t

AZ

Maximum time allowed for output drivers to release (from asserted or negated)

t

ZAH

Minimum delay time required for output

t

ZAD

drivers to assert or negate (from released)

t

ENV

Envelope time (from DMACK- to STOP and HDMARDY- during data in burst initiation and from DMACK

to STOP during data out burst initiation)

t

RFS

Ready-to-final-STROBE time (no STROBE edges shall be sent this long after negation of DMARDY-)

t

RP

Ready-to-pause time (that recipient shall wait to pause after negating DMARDY-)

t

IORDYZ

Maximum time before releasing IORDY

t

ZIORDY

Minimum time before driving IORDY

t

ACK

Setup and hold times for DMACK- (before assertion or negation)

t

SS

Time from STROBE edge to negation of DMARQ or assertion of STOP (when sender terminates a burst)