DS206 August 31, 2005 www.xilinx.com 1

Product Specification v3.0.151

© 2005 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective

owners. Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx

makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly

disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from

claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

co.com

Features

• Fully PCI 3.0-compliant LogiCORE™, 32-bit, 66/33

MHz interface

• Customizable, programmable, single-chip solution

• Pre-defined implementation for predictable timing

• Incorporates Xilinx Smart-IP™ technology

• 3.3V operation at 0-66 MHz

• 5.0V operation at 0-33 MHz

• Fully verified design tested with Xilinx proprietary

testbench and hardware

• Available through the Xilinx CORE Generator™

v7.1i or higher

• CardBus compliant

• Supported initiator functions:

- Configuration read, configuration write

- Memory read, memory write, MRM, MRL

- Interrupt acknowledge, special cycles

- I/O read, I/O write

• Supported target functions:

- Type 0 configuration space header

- Up to three base address registers (MEM or I/O

with adjustable block size from 16 bytes to 2 GB)

- Medium decode speed

- Parity generation, parity error detection

- Configuration read, configuration write

- Memory read, memory write, MRM, MRL

- Interrupt acknowledge

- I/O read, I/O write

- Target abort, target retry, target disconnect

0

PCI32 Interface v3.0

DS206 August 31, 2005

00

Product Specification v3.0.151

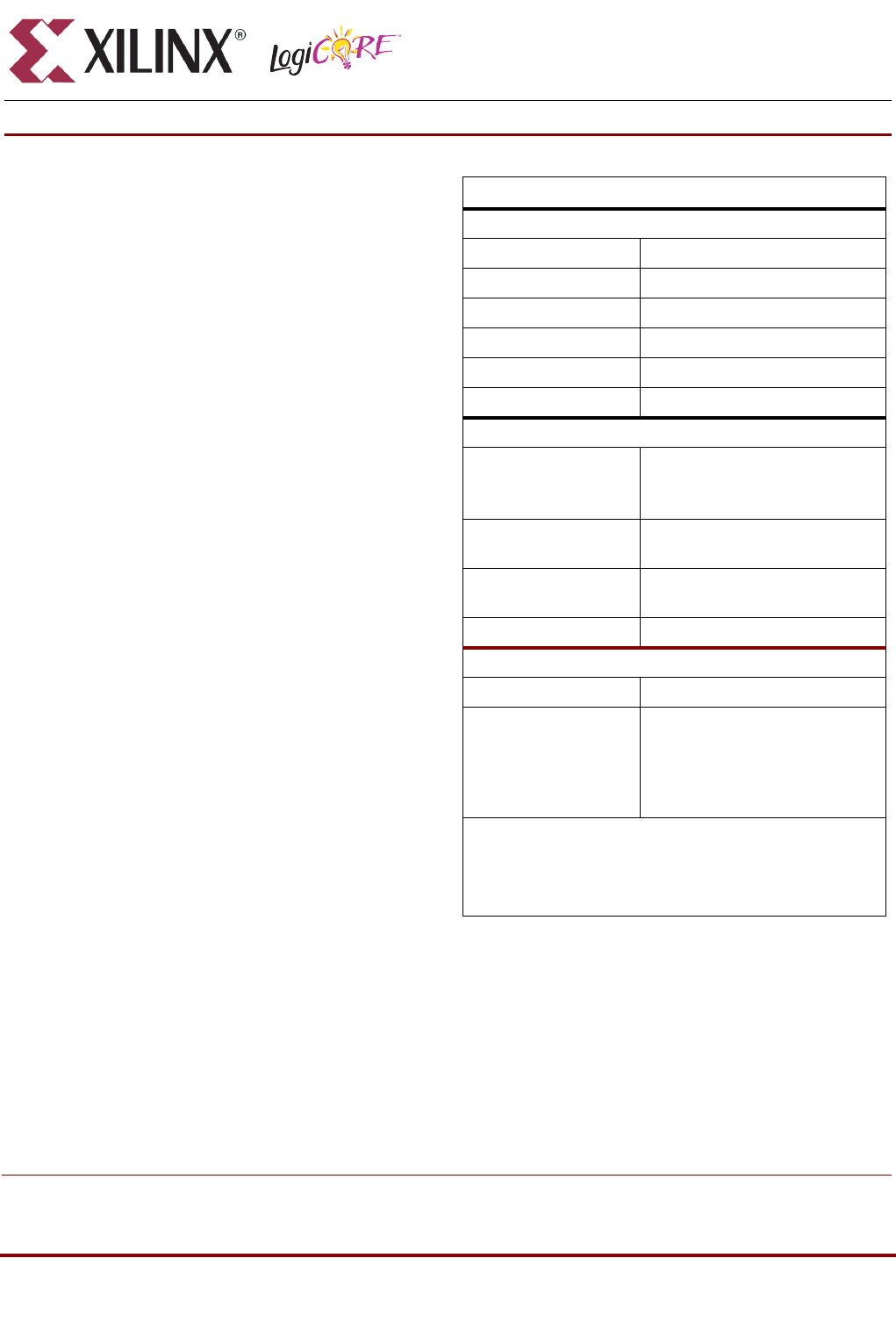

LogiCORE Facts

PCI32 Resource Utilization

(1)

Slice Four Input LUTs 553

Slice Flip-Flops 566

IOB Flip-Flops 97

IOBs 50

TBUFs 288

GCLKs 1

(2)

Provided with Core

Documentation

PCI32 Product Specification

PCI Getting Started Guide

PCI User Guide

Design File Formats

Verilog/VHDL Simulation Model

NGO Netlist

Constraints Files

User Constraints File (UCF)

Guide File (NCD)

Example Design Verilog/VHDL Example Design

Design Tool Requirements

Xilinx Tools v7.1i Service Pack 4

Tested Entry and

Verification Tools

(3)

Synplicity Synplify

Xilinx XST

(4)

Model Technology ModelSim

Exemplar LeonardoSpectrum

Cadence NC-Verilog

Xilinx provides technical support for this LogiCORE product when

used as described in the PCI Getting Started Guide and PCI User

Guide. Xilinx cannot guarantee timing, functionality, or support of

product if implemented in devices not listed, or if customized

beyond that allowed in the product documentation.