2-6 Service Guide

The 82371AB PCI ISA IDE Xcelerator (PIIX4) is a multi-function PCI device implementing a PCI-to-

ISA bridge function, a PCI IDE function, a Universal Serial Bus host/hub function, and an Enhanced

Power Management function. As a PCI-to-ISA bridge, PIIX4 integrates many common I/O functions

found in ISA-based PC systems—two 82C37 DMA Controllers, two 82C59 Interrupt Controllers, an

82C54 Timer/Counter, and a Real Time Clock. In addition to compatible transfers, each DMA

channel supports Type F transfers. PIIX4 also contains full support for both PC/PCI and Distributed

DMA protocols implementing PCI-based DMA. The Interrupt Controller has Edge or Level sensitive

programmable inputs and fully supports the use of an external I/O Advanced Programmable

Interrupt Controller (APIC) and Serial Interrupts. Chip select decoding is provided for BIOS, Real

Time Clock, Keyboard Controller, second external microcontroller, as well as two Programmable

Chip Selects. PIIX4 provides full Plug and Play compatibility. PIIX4 can be configured as a

Subtractive Decode bridge or as a Positive Decode bridge. This allows the use of a subtractive

decode PCI-to-PCI bridge such as the Intel 380FB PCIset which implements a PCI/ISA docking

station environment.

PIIX4 supports two IDE connectors for up to four IDE devices providing an interface for IDE hard

disks and CD ROMs. Up to four IDE devices can be supported in Bus Master mode. PIIX4 contains

support for “Ultra DMA/33” synchronous DMA compatible devices.

PIIX4 contains a Universal Serial Bus (USB) Host Controller that is Universal Host Controller

Interface (UHCI) compatible. The Host Controller’s root hub has two programmable USB ports.

PIIX4 supports Enhanced Power Management, including full Clock Control, Device Management for

up to 14 devices, and Suspend and Resume logic with Power On Suspend, Suspend to RAM or

Suspend to Disk. It fully supports Operating System Directed Power Management via the Advanced

Configuration and Power Interface (ACPI) specification. PIIX4 integrates both a System

Management Bus (SMBus) Host and Slave interface for serial communication with other devices.

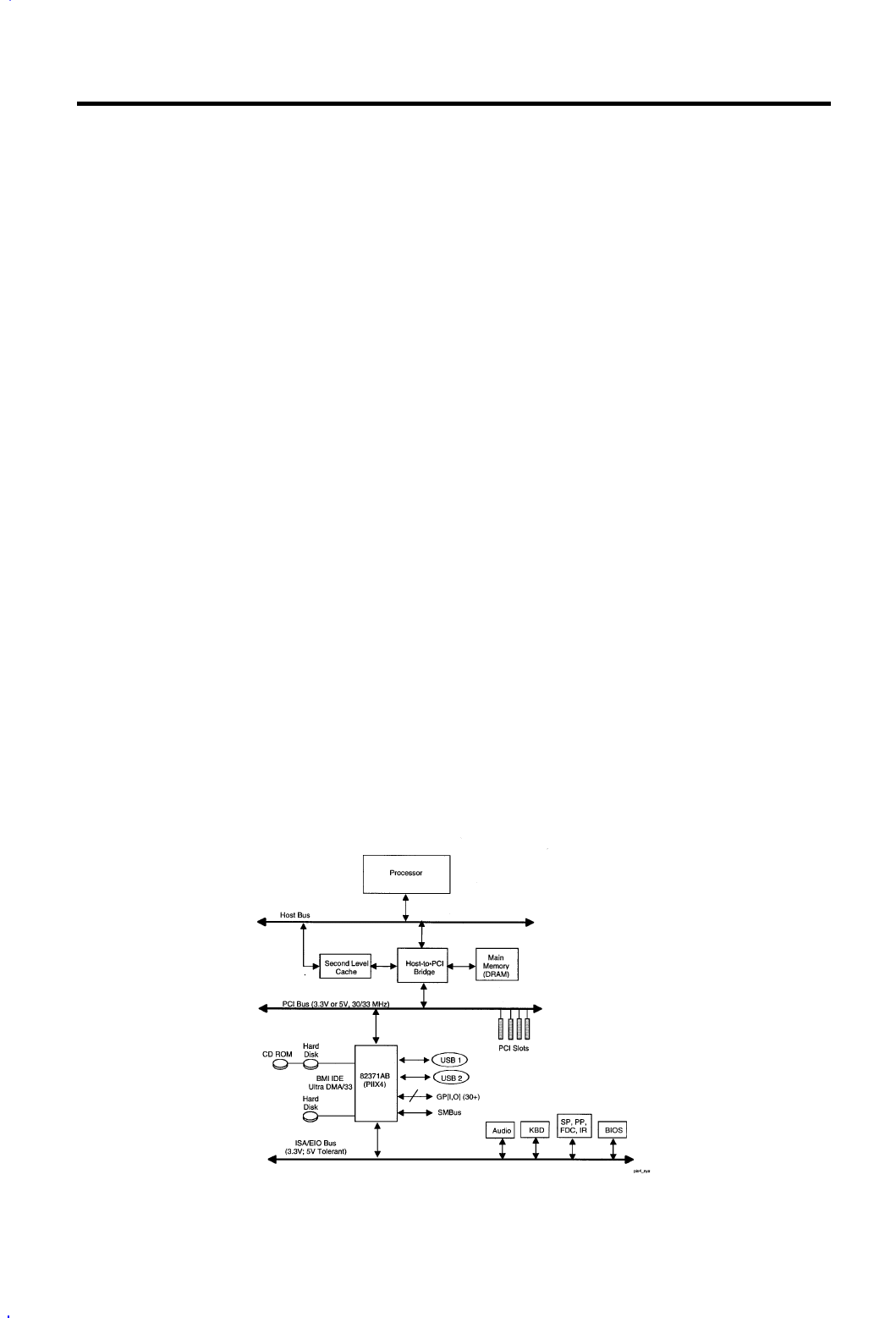

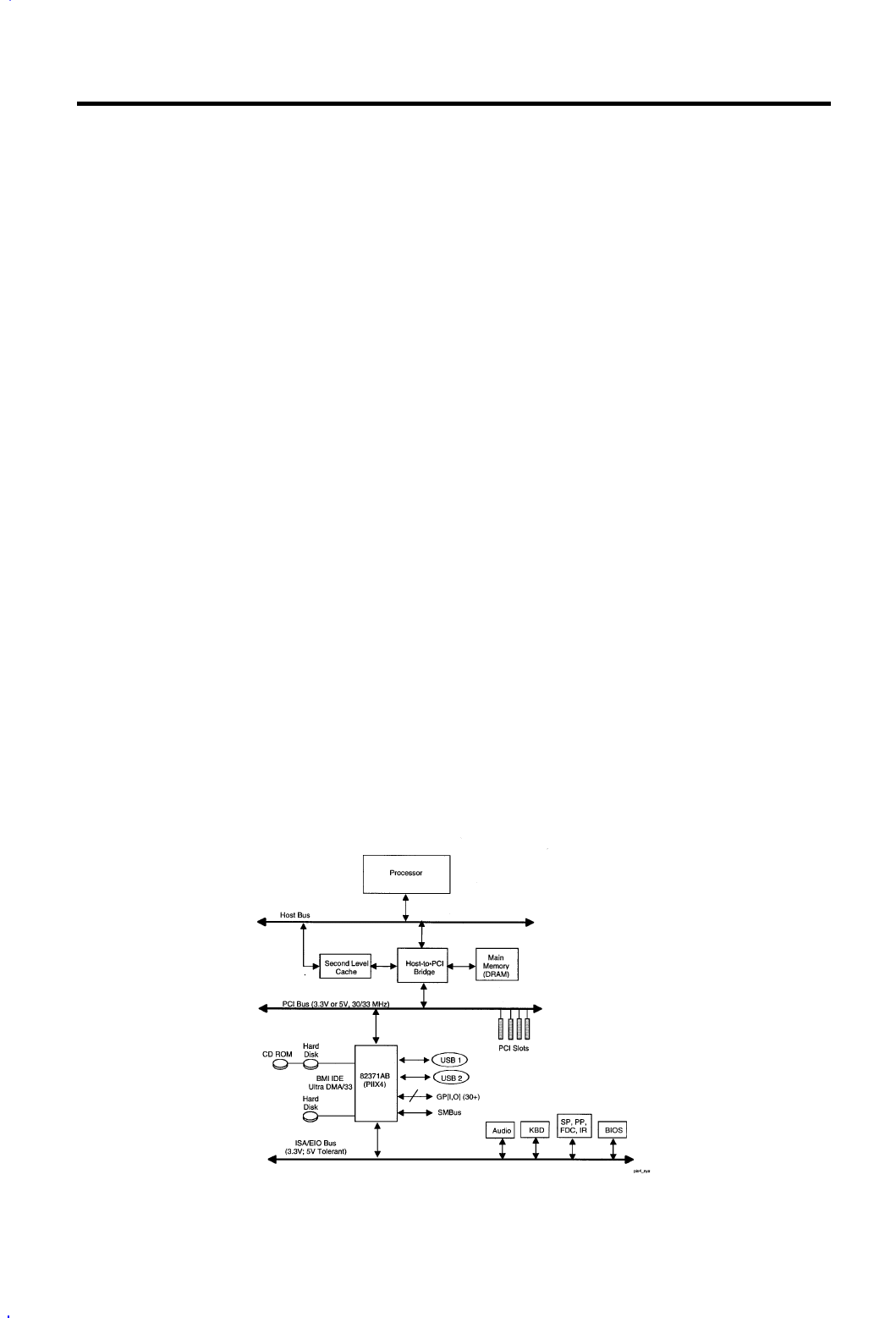

2.2.2 Architecture Block Diagram

The following is the architectural block diagram of the PIIX4 with respect to its implementation in this

notebook computer.

Figure 2-1 PIIX4 Architecture Block Diagram