Intel® PXA27x Processor Family Power Requirements

Application Note 19

4.1 Power Enable (PWR_EN)

PWR_EN is an active-high output from the PXA27x processor (input to the PMIC) that enables the

external core power supplies (VCC_CORE, VCC_SRAM, and VCC_PLL). De-asserting

PWR_EN informs the external regulator that the processor is going into sleep mode, and that the

low-voltage core power supplies are to be shut down.

The PMIC turns on the core (low-voltage) supplies in response to PWR_EN assertion to resume

normal operation. The power controller must preserve, during sleep or deep sleep, the previous

state of its regulators including the voltage for the core, so that on resumption of core power, the

regulators return to their last known voltage levels.

4.2 System Power Enable (SYS_EN) / GPIO<2>

SYS_EN is an active-high output from the PXA27x processor (input to the PMIC) that enables the

external system power supplies. De-asserting SYS_EN informs the power supply that the processor

is going into deep-sleep mode, and that the high-voltage system power supplies (VCC_IO,

VCC_LCD, VCC_MEM, VCC_USIM, VCC_BB, and VCC_USB) are to be shut down. Assertion

and de-assertion of SYS_EN occurs in the correct sequence with PWR_EN to ensure the correct

sequencing of power supplies when powering on and off the various voltage domains.

To resume normal operation, the PMIC first turns on the system I/O (high-voltage) supplies in

response to SYS_EN assertion and then turns on the core (low-voltage) supplies in response to

PWR_EN assertion. The power controller must return all system I/O voltages to their pre-deep

sleep mode levels.

4.3 Power Manager I

2

C Clock (PWR_SCL) / GPIO<3>

The PWR_SCL signal is the power manager I

2

C clock in to the external PMIC. The I

2

C serial bus

must operate at a minimum 40 kHz and (optionally) be able to operate at a 160 kHz clock rate.

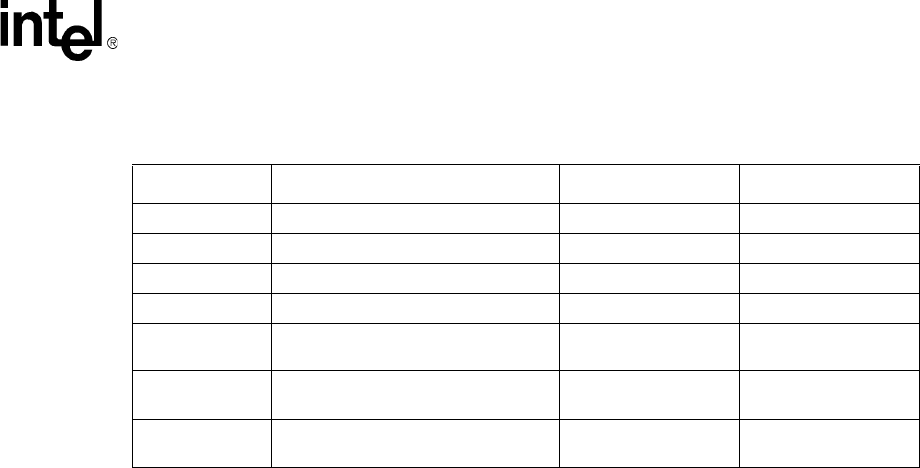

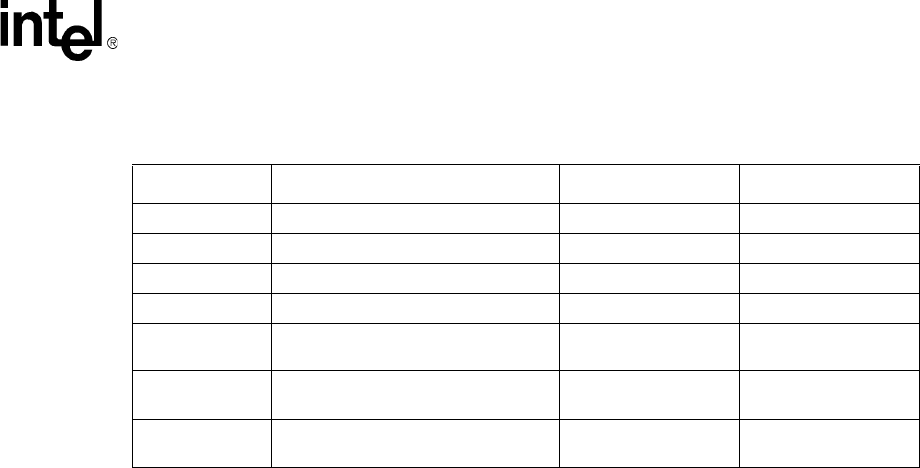

Table 8. Power Controller Interface Signals

Signal Definition Active State Signal Direction

1

PWR_EN Power enable high Output

SYS_EN System enable high Output

PWR_SCL I

2

C bus clock Clock Output

PWR_SDA I

2

C bus data — Bidirectional

nRESET

Forces an unconditional hardware

reset

low Input

nBATT_FAULT

Indicates main battery removed or

discharged

low Input

nVDD_FAULT

Indicates one or more supplies are out

of regulation

low Input

NOTE: 1. Input and output refers to the signal direction from the standpoint of the PXA27x processor