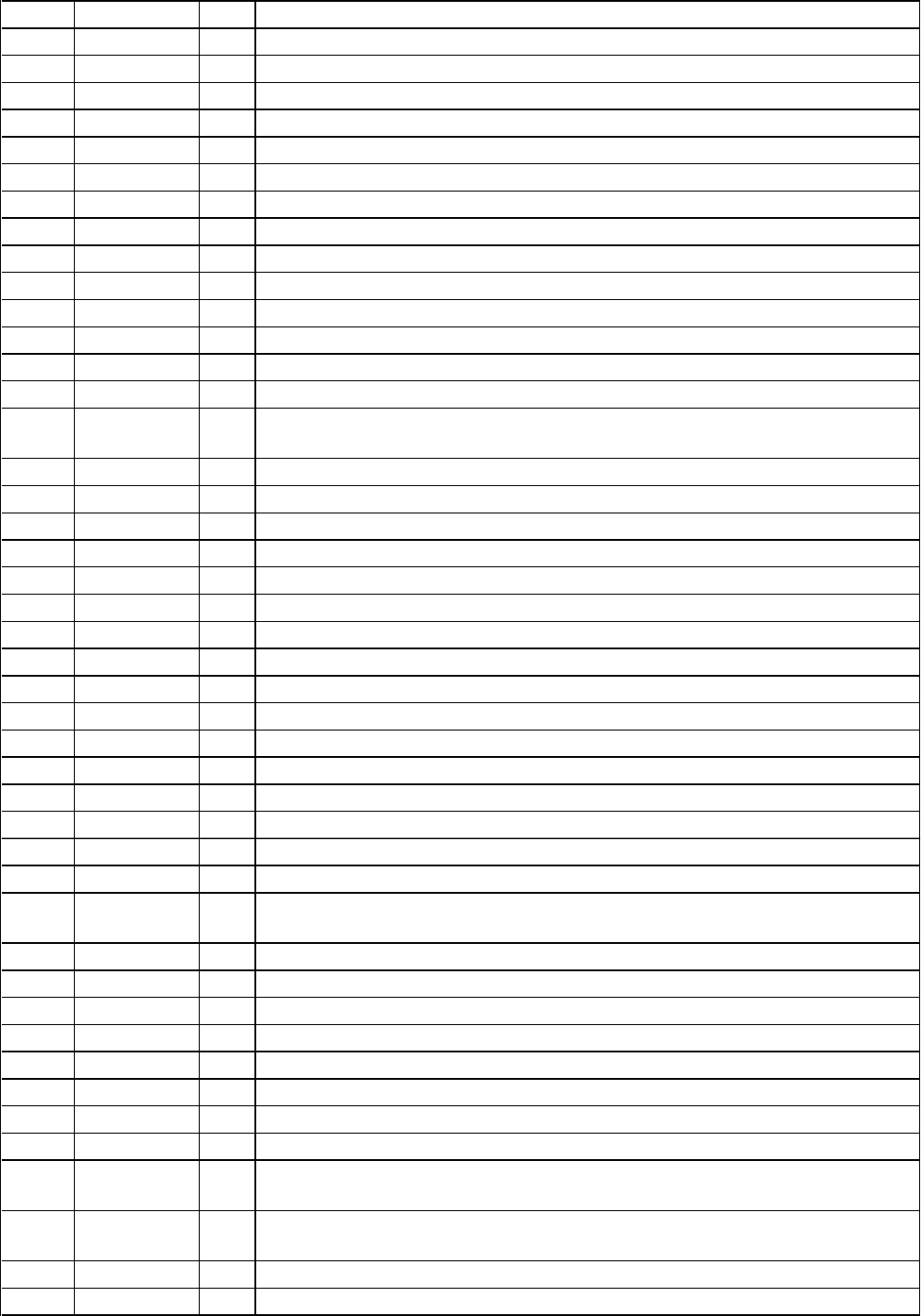

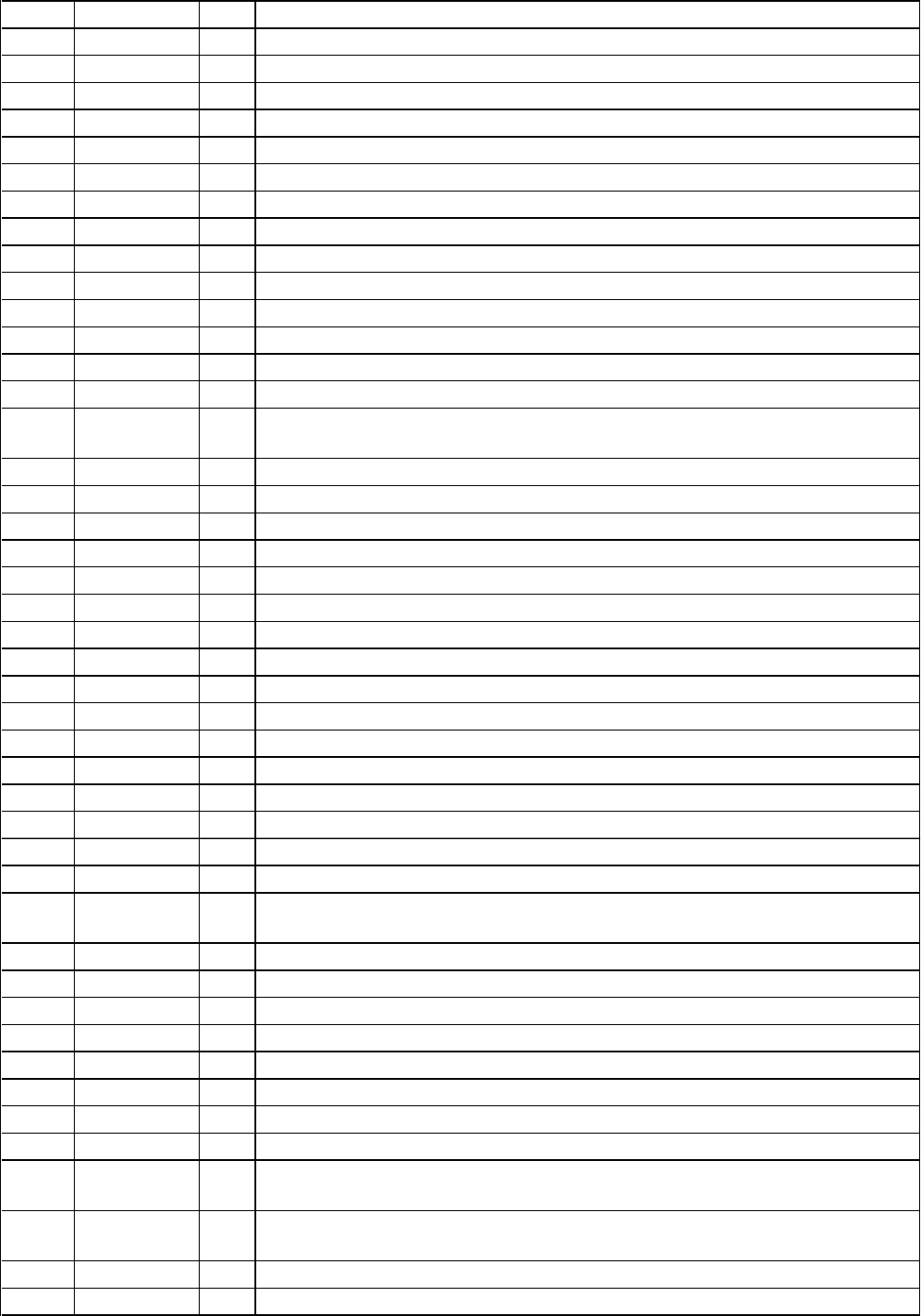

35

MZ-R900

Pin Name

I/O Description

47 FE I Focus error signal input from RF amp (IC501)

48 AUX1 I Support signal (I

3 signal/temperature signal) input terminal (A/D input)

49 VC I Middle point voltage (+1.2V) input terminal

50 ADIO O Monitor output of A/D converter input signal Not used (open)

51 ADRT I A/D converter the upper limit voltage input (fixed at “H” in this set)

AVD2

—

Power supply terminal (for the analog) (+2.4V)

AVS2

—

Ground terminal (for the analog)

ADRB

I

A/D converter the lower limit voltage input (fixed at “L” in this set)

SE

I

Sled error signal input terminal Not used ( fixed at “L”)

TE

I

Tracking error signal input from RF amp (IC501)

DCHG

—

Connecting analog power supply of the low impedance (fixed at “H” in this set)

APC

I

Error signal input for the laser automatic power control Not used (fixed at “H”)

DSPVDD0

—

Power supply terminal (for DSP block) (+1.5V)

DSPVSS0

—

Ground terminal (for DSP block)

XTSL

I

Input terminal for the frequency set up of the system clock “L”: 45.1584MHz,

“H”: 22.5792MHz (fixed at “L” in this set)

DIN1

I

Input terminal of the record system digital audio signal

DOUT

O

Output terminal of the playback system digital audio signal Not used (open)

DAPWMLP O D/A converter PWM output (L-CH right phase) Not used (open)

DAPWMLN

O

D/A converter PWM output (L-CH reverse phase) Not used (open)

DAPWMRP O D/A converter PWM output (R-CH right phase) Not used (open)

DADT O Audio data output to the external A/D, D/A converter (IC301)

ADDT

I

Data signal input from the external A/D, D/A converter (IC301)

LRCK O L/R sampling block signal (44.1KHz) output to the external A/D, D/A converter (IC301)

XBCK O Bit clock signal (2.8224MHz) output to the external A/D, D/A converter (IC301)

FS256

O

11.2896MHz clock signal output to the external A/D, D/A converter (IC301)

MVCI

I

Vibrate input for the digital in PLL from the external VCO Not used (fixed at “L”)

DSPVDD1

—

Power supply terminal (for DSP block) (+1.5V)

ADFG

I

ADIP duplex FM signal (20.05±1KHz) input from RF amp (IC501)

F0CNT

O

Filter cut off control signal output Not used

DIFVDD0

—

Power supply terminal (for DSP I/F) (+2.3V)

DIFVSS0

—

Ground terminal (for DSP I/F)

APCREF O

Control signal output to the reference voltage generation circuit for the laser automatic power

control

LDDR O PWM signal output for the laser automatic power control Not used (open)

TRDR O Tracking servo drive PWM signal output (–) to the motor driver (IC551)

TFDR O Tracking servo drive PWM signal output (+) to the motor driver (IC551)

FFDR O Focus servo drive PWM signal output (+) to the motor driver (IC551)

FRDR O Focus servo drive PWM signal output (–) to the motor driver (IC551)

MCUVDD1

—

Power supply terminal (for the microcomputer block) (+1.5V)

FGIN I FG signal input terminal for the spindle servo Not used (open)

FS4 O 176.4MHz clock signal output to the power control (IC601, IC901)

SPRD/SPDU/

RTG0

O Spindle servo drive PWM signal output terminal (–) to the motor driver (IC551)

SPFD/SPVS/

PWM3

O Spindle servo drive PWM signal output (+)

SPDV/RTG1 O Spindle motor drive control signal output (V)/RTG output 1 to the motor driver (IC551)

SPDW/RTG2 O Spindle motor drive control signal output (W)/RTG output 2 to the motor driver (IC551)