PCI-COM422/4 Manual

Page 5-2

Manual MPCICOM422-4.E1b

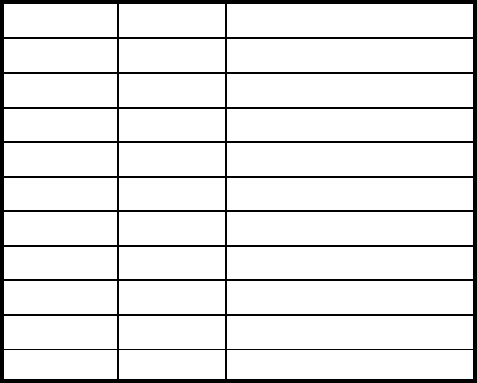

On the PCI-COM422/4 card, the UART clock frequency is 1.8432 MHz. On the next page is a table

for the popular divisor frequencies:

Baud Rate Divisor Max Diff. Cable Length *

115200 1 2200 ft

57600 2 4000 ft

38400 3 4000 ft

28800 4 4000 ft

19200 6 4000 ft

14400 8 4000 ft

9600 12 4000 ft

4800 24 4000 ft

2400 48 4000 ft

1200 96 4000 ft

Table 5-1: Baud Rate Divisor Values

*These are theoretical maximums based on typical conditions and good quality cables based on the

EIA 485 and EIA 422 standard for balanced differential drivers. RS-232 communication lines have

a maximum length of 50 feet, regardless of speed.

In C, the code to set the chip to 9600 baud is:

outportb(BASEADDR, 0x0C);

outportb(BASEADDR +1,0);

The second initializing step is to set the Line Control Register at Base Address +3. This register

defines word length, stop bits, parity, and the DLAB.

Bits 0 and 1 control word length and allow word lengths from 5 to 8 bits. Bit settings are

extracted by subtracting 5 from the desired word length.

Bit 2 determines the number of stop bits. There can be either one or two stop bits. If Bit 2 is set

to 0, there will be one stop bit. If Bit 2 is set to 1, there will be two stop bits.

Bits 3 through 6 control parity and break enable. They are not commonly used for

communications and should be set to zeroes.

Bit 7 is the DLAB discussed earlier. It must be set to zero after the divisor is loaded or else there

will be no communications.