Chapter 7 Advanced 400 Front-Side Bus AMD Athlon™ XP Processor Model 10 Specifications 27

26237C—May 2003 AMD Athlon™ XP Processor Model 10 Data Sheet

Preliminary Information

7.3 Advanced 400 FSB AMD Athlon™ System Bus

AC Characteristics

The AC characteristics of the AMD Athlon system bus of this

processor are shown in Table 7. The parameters are grouped

based on the source or destination of the signals involved.

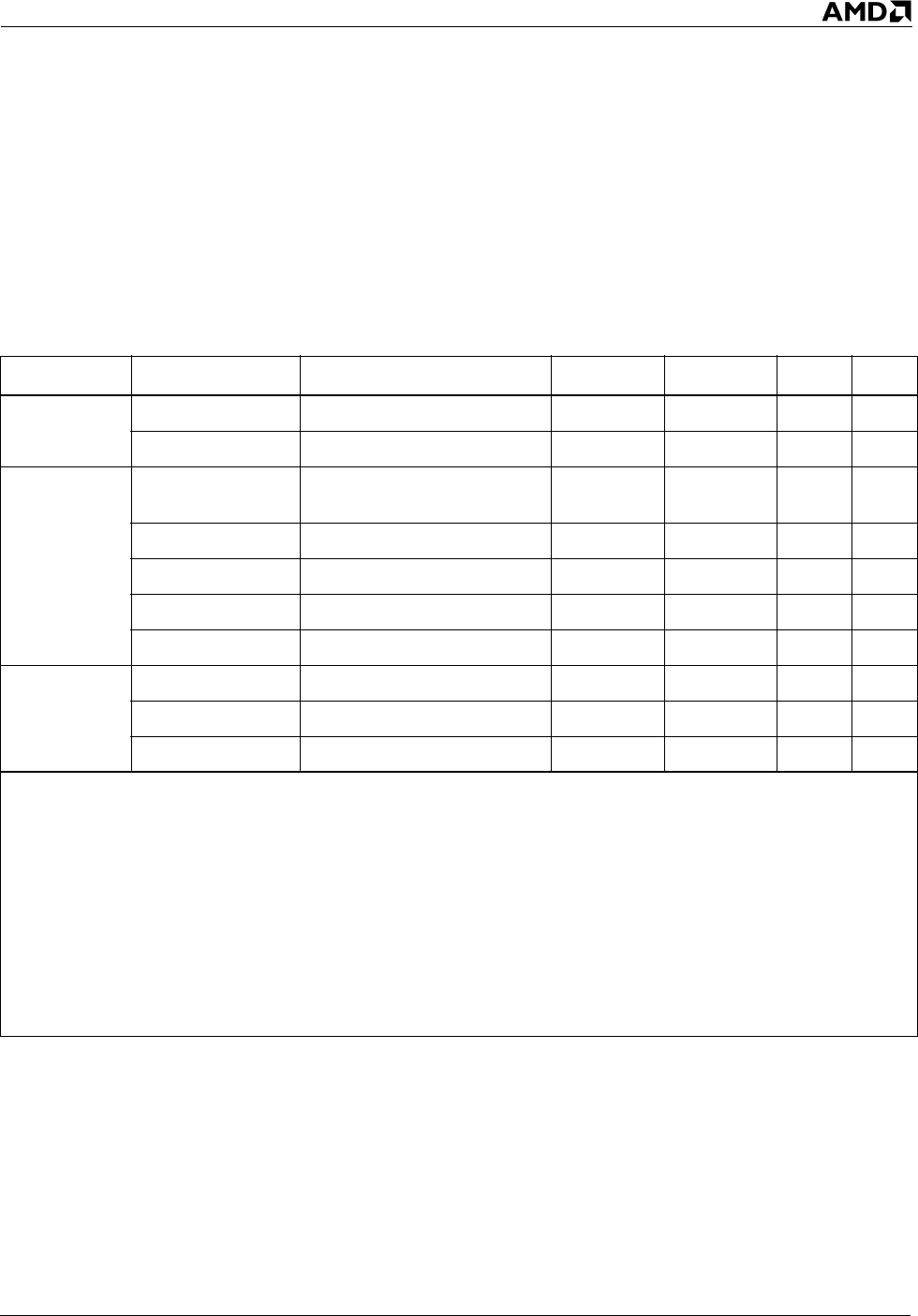

Table 7. Advanced 400 FSB AMD Athlon™ System Bus AC Characteristics

Group Symbol Parameter Min Max Units Notes

All Signals

T

RISE

Output Rise Slew Rate 1 3 V/ns 1

T

FALL

Output Fall Slew Rate 1 3 V/ns 1

Forward

Clocks

T

SKEW-DIFFEDGE

Output skew with respect to a

different clock edge

–500ps2

T

SU

Input Data Setup Time 300 ps 3

T

HD

Input Data Hold Time 300 ps 3

C

IN

Capacitance on input clocks 4 25 pF

C

OUT

Capacitance on output clocks 4 12 pF

Sync

T

VAL

RSTCLK to Output Valid 800 2000 ps 4, 5

T

SU

Setup to RSTCLK 500 ps 4, 6

T

HD

Hold from RSTCLK 500 ps 4, 6

Notes:

1. Rise and fall time ranges are guidelines over which the I/O has been characterized.

2. T

SKEW-DIFFEDGE

is the maximum skew within a clock forwarded group between any two signals or between any signal and its

forward clock, as measured at the package, with respect to different clock edges.

3. Input SU and HD times are with respect to the appropriate Clock Forward Group input clock.

4. The synchronous signals include

PROCRDY, CONNECT, and CLKFWDRST.

5. T

VAL

is RSTCLK rising edge to output valid for PROCRDY. Test Load is 25 pF.

6. T

SU

is setup of CONNECT/CLKFWDRST to rising edge of RSTCLK. T

HD

is hold of CONNECT/CLKFWDRST from rising edge of

RSTCLK.