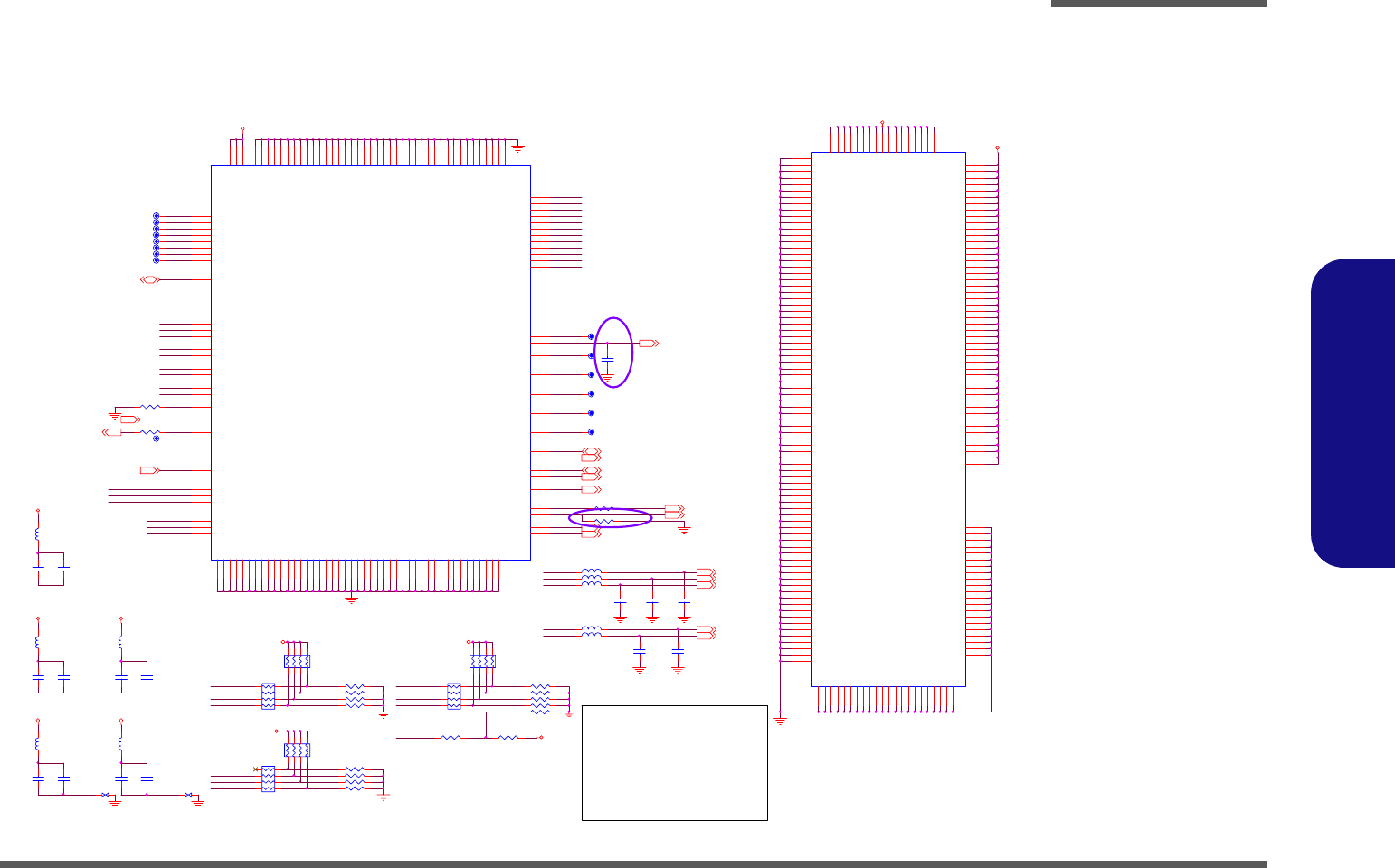

Schematic Diagrams

VN896-4 B - 9

B.Schematic Diagrams

VN896-4

Sheet 8 of 40

VN896-4

Z0813

NB_DDC_DATA 24

3.3VS

NB_ENAVDD 24

DVP0VS 24

AR

VCCDAC1

PDVP1DE

Z0801

SW1_4 FD7 =>GFX Clock Select(VCK/LCDCK/ECK)

NB_LVDSDATA 24

R206

80.6_1%_06

3.3VS

GUICK2

R193 0_04

ADD*47P? ? NB

FOR EMI 951124

DVP2D09

L_BKLTEN 24

DVP2D00

SW1_2 FD5 =>Dedicated DVI Port Configuration

RN3

1K_8P4R_06

1

2

3

4 5

6

7

8

DVP2D04

RN4

1K_8P4R_06

1

2

3

4 5

6

7

8

AGP_BUSY # 17

VSY NC

Z0817

C285

1000P_50V_06

R196 0_04Z0807

DVP2D03

C291

1000P_50V_06

AG

R210 SE DEL

Enable spread

spectrum

C960124

AB

R198 *0_04

NB_VSYNC 24

VD15

0: Refer Internal PLL(Default)

1: From External

Z0811

1.5VS

DVPDET

S9 S?

2 1

VCCPLL2

DACGND

DVP2D06

PDVP1HS

RN7

10K_8P4R_06

1

2

3

4 5

6

7

8

3.3VS

Z0805

DVP2D01

Z0806

C332

1U_10V_06

3.3VS

3.3VS

DVP2D07

VPAR17

Z0802

R209 22_04

SW1_5 FD10 =>CPUCK/M CK Clock Select

ENAVEE24

Z0812

R199 *0_04

R235 0_06

3.3VS

Z0814

NB_DDC_CLK 24

VD10

DVP2D08

VCCDAC2

DVP0VS

NB_GREEN 24

DISPCLKO

DACGND

FB6

HCB2012KF-121T30_08

R218 10K_04

3.3VS

VD14

GNDPLL

DVP2D02

DVP2D02

GND

R221 0_04

DVP2D09

R200 0_04

HSYNC

VD08

Z0816

HSYNC

R190 0_04

NB_BLUE 24

DVP2D01

GNDPLL

RN6

10K_8P4R_06

1

2

3

4 5

6

7

8

DVP2D11

0: From NB(Default)

1: From External

DACGND

L35 HCB1608KF-121T25_06

PDVP1CLK

C289

1000P_50V_06

DISPCLKO 24

DACGND

C276

1000P_50V_06

VD11

Z0809

SW1_3 FD6 =>Dedicated DVI Port Selection

DVP2D05

VCCPLL1

L36 HCB1608KF-121T25_06

0: TMDS

1: TV

Encoder

3.3VS

VD09

Z0804

NB_LVDSCLK 24

VCCPLL1

C325

1U_10V_06

FB5

HCB2012KF-121T30_08

C271

22P_50V_06

S7 S?

2 1

C288

22P_50V_06

FD[0:1:2:3:8:9:11] Reserved

DISPCLKI 24

R191 0_04

AR

DVP2DET

DVP2D04

R194 0_04

VCCPLL2

RN2

*1K_8P4R_06

1

2

3

4 5

6

7

8

R197 0_04

L34 HCB1608KF-121T25_06

NB_RED 24

BGA5E

P4M900

T24

R24

AE14

AJ10

AJ12

AK10

AK11

AJ11

AJ23

AJ20

AJ19

AG36

AG33

AG31

AG30

AG5

AG4

AG2

Y5

Y6

Y7

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

Y22

Y23

Y30

Y32

Y34

AA2

AA4

AA5

AA7

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AA23

AA31

AA33

AA35

AB2

AB4

AB5

AB7

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB22

AB21

AC2

AC5

AC6

AC7

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

AC23

AD2

AD5

AD32

AE2

AE5

AE32

AE34

AF2

AF3

AF5

AB23

AJ13

AJ14

AK9

AK12

AK13

AK15

AL8

AL9

AL10

AL11

AL12

AL14

AM7

AM8

AM9

AM10

AM11

AG3

Y36

N22

N23

N24

P24

M17

M18

M19

N18

N19

N20

N21

AJ33

AK17

AK18

AK22

AK32

U24

V24

W24

Y24

AM12

AM13

AN19

AN17

AN13

AN12

AM36

AL33

AL24

AL22

AL19

AL17

AL16

AL15

AK36

AN35

AP2

AP16

AP22

AP24

AR16

AR23

AR35

AT4

AT17

AT20

AT22

AT23

AT11

AT14

AN8

AN9

AN10

AN11

AP8

AP9

AP10

AP11

AR7

AR8

AR9

AR10

AT7

AT8

AT9

AT10

AL3

AL7

AM2

AP3

AP6

AR2

AR6

AN7

AP7

AE16

AE18

AE20

AE21

AE22

VTT

VTT

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

GND

GND

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

GND

GND

GND

GND

GND

VTT

VTT

VTT

VTT

VCC15

VCC15

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

GND

GND

GND

GND

GND

GND

GND

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

R217 *1K_04

NB_HSYNC 24

VN896

H11

D10

C11

C10

E10

G10

F11

C9

E8

B7

F9

C7

C6

A5

B9

D9

A9

E11

B10

C8

G13

A7

E13

A13

A12

A16

A15

A14

B16

B15

B14

B13

B12

C14

D14

E14

E12

F12

H12

G12

A11

B11

AC35

C13

H13

B8

A6

D12

N15

N16

N17

P21

P22

P35

U18

U19

U20

U21

U22

U23

U31

U33

V2

V5

V7

V14

V15

V16

V17

V18

V19

V20

V22

V21

V23

V30

V35

W2

W5

W7

W14

W15

W16

W17

W18

W19

W20

W21

W22

W23

Y2

R5

R6

R7

R14

R15

R16

R17

R18

R19

R20

R21

R23

R30

R31

T2

T4

T5

T7

T14

T15

T16

T17

T18

T19

T20

T21

T22

T23

T34

T36

U2

U5

U7

U14

U15

U16

U17

R2

R4

P23

R22

P33

AM1

AM3

AT5

AM6

AL2

AL1

AN6

AT6

AM4

D13

F13

C12

DVP2D00

DVP2D01

DVP2D02

DVP2D03

DVP2D04

DVP2D05

DVP2D06

DVP2D07

DVP2D08

DVP2D09

DVP2D10

DVP2D11

DVPDET

DVP0VS

DVP2CLK

DVP2DE

DVP2DET

DVP2HS

DVP2VS

SPCLK1

SPCLK2

SPD1

SPD2

VCCA33DAC1

VCCA33DAC2

VCCA33PLL1

VCCA33PLL2

VCCA33PLL3

GNDAPLL

GNDAPLL

GNDAPLL

GNDADAC

GNDADAC

AR

AG

AB

HSYNC

VSY NC

DISPCLKO

DISPCLKI

ENBLT

ENVDD

BUSY#

RSET

INTA#

GPO0

GPOUT

XI N

VCC33GFX

VCC33GFX

VCC33GFX

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VD08

VD09

VD10

VD11

VD12

VD13

VD14

VD15

VPAR

GND

GND

GND

R195 0_04

L37 HCB1608KF-121T25_06

PCI_INTA#15,19

AB

C326

22P_50V_06

C278

22P_50V_06

VCCDAC1

R201 0_04

VSYNC

Z0815

DVP2D10

0: Disable

1: Enable

FB7

HCB2012KF-121T30_08

GND

DVP2D06

GNDPLL

DVP2D08

AG

GNDPLL

FB10

HCB2012KF-121T30_08

DVP2D07

SW1_1 FD4 =>Port Muxing

GFX power up strapping setting:

R210 4.7K_04

0: Two 12-bit DVI interface

1: One 24-bit Panel

interface

Z0803

DVP2D03

C283

1U_10V_06

1.05VS

GNDPLL

VCCDAC2

VD12

DVP2D10

PDVP1VS

DISPCLKI

3.3VS

GNDPLL

Z0810

DVP2D11

FB8

HCB2012KF-121T30_08

C293

22P_50V_06

C265

1U_10V_06

R192 0_04

C784

*47P_50V_04

VCCPLL3

3.3VS

C286

1U_10V_06

DVP2D05

VCCPLL3

DVP2D00

VD13

RN5

10K_8P4R_06

1

2

3

4 5

6

7

8

L39 HCB1608KF-121T25_06

C329

1000P_50V_06

Z0808