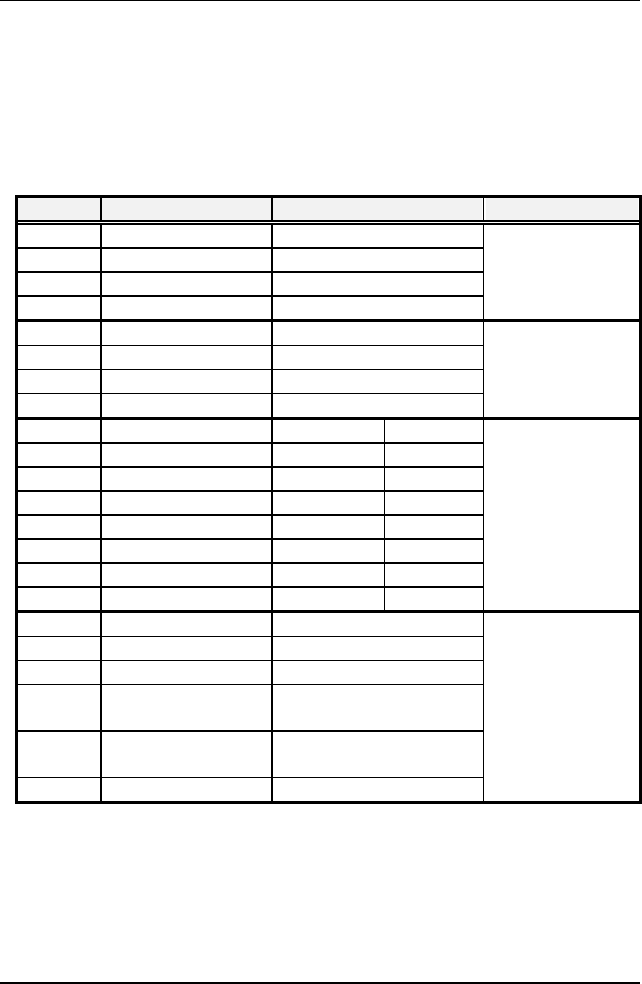

Registers Format • 21

3.2 I/O Address Map

All the 48H registers are 8 bits. The users can access these registers

only by 8 bits I/O instructions. The following ta ble shows the registers map,

including descriptions and their offset addresses relative to the base

address. Please refer to the chapter 4 for more detailed operation of every

registers.

Offset Write Read Boards

0x00 P1A P1A PCIDIO 24H

0x01 P1B P1B PCIDIO 48H

0x02 P1C P1C PCIDIO 96H

0x03 P1Ctrl Not used

0x04 P2A P2A PCIDIO 48H

0x05 P2B P2B PCIDIO 96H

0x06 P2C P2C

0x07 P2Ctrl Not used

0x08 P3A P3A P1AE

(1)

PCIDIO 96H

0x09 P3B P3B P1BE

(1)

0x0A P3C P3C P1CE

(1)

(1)

doesn't apply to

0x0B P3Ctrl Not used Not used PCIDIO series

0x0C P4A P4A P2AE

(1)

0x0D P4B P4B P2BE

(1)

0x0E P4C P4C P2CE

(1)

0x0F P4Ctrl Not used Not used

0x10 Timer/Counter #0 Timer/Counter #0 PCIDIO 24H

0x11 Timer/Counter #1 Timer/Counter #1 PCIDIO 48H

0x12 Timer/Counter #2 Timer/Counter #2 PCIDIO 96H

0x13

Timer/Counter

Mode Control

Timer/Counter

Mode Status

not applicable

0x20

ISC: Interrupt

Source Control

Not used

0x30 Clear Interrupt Not used