HARDWARE

2-10

CPCI-824 User’s Manual

Revision 1.0, January 2006

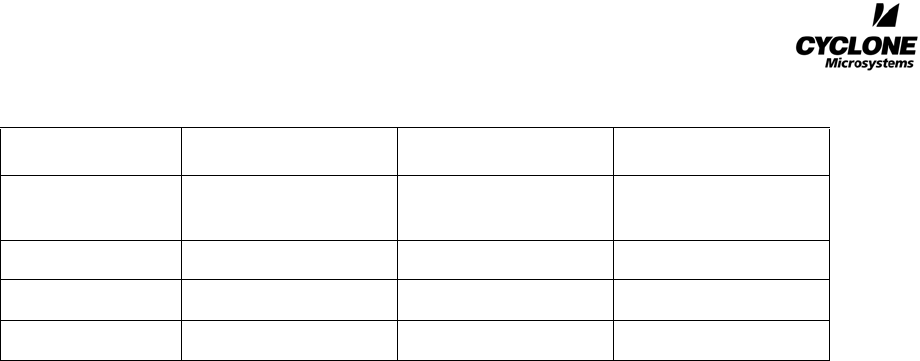

Table 2-7. I

2

C Device Addresses

2.10.1 SDRAM EEPROM

The EEPROM located on the DDR SDRAM module contains identification and configuration infor-

mation. Breeze code will read this information on power-up and will properly configure the

PPC440GX processor to the SDRAM type. No user intervention is required.

2.10.2 Temperature Sensors

The LM75 temperature sensors have overtemperature trip points that will trigger an interrupt when

crossed. The sensors have been placed on the board U1 & U14 and share an interrupt line to the

processor. Polling the two devices will be required to determine which part has triggered the interrupt.

The sensors are placed in interrupt mode by the Breeze initialization code. The default overtemperature

point is 80 degrees Celsius. The sensors can be read for a temperature reading at any time, reading after

an interrupt clears the interrupt. The sensor will not interrupt again until the temperature has dropped

below the hysteresis value (default is 75 degrees Celsius) and risen again passed the trip point. Consult

the LM75 data sheet for more details on programming the temperature sensors.

2.10.3 Serial EEPROM

The first time a CPCI-820 is powered up, initial conditions are read from a serial EEPROM connected

to the I2C bus. The device is read during reset. Initially, the serial EEPROM is disabled and the

processor powers up in a default state. Once the board is programmed and the serial EEPROM is

programmed, then subsequent power ups will use the data stored.

2.10.4 Phase Lock Loop Clock Driver

The PPC440GX memory controller generates a single differential pair memory clock for the DDR

SDRAM devices. The CDCV850 is a low skew, low jitter, zero delay buffer that distributes the differ-

ential clock to the three input pairs of the 200 pin SoDIMM.

2.11 JTAG EMULATOR SUPPORT

The CPCI-824 provides a joint test action group JTAG emulator interface at J27 for XScale compatible

emulators. The JTAG emulator interface connects to the JTAG port of the IOP331 processor and has the

ability to assert a reset to the secondary PCI bus. The JTAG emulator header definition is shown in

Table 2-8

Designator Device Function Address

J10

DDR SDRAM

EEPROM SODIMM

Memory

Configuration

10100011

U13 LM75 Temperature Sensor 1001000x

U1 LM75 Temperature Sensor 1001001x

U16 24C08-LV Serial EEPROM 1010000x