PRELIMINARY

CY14B102L, CY14B102N

Document #: 001-45754 Rev. *B Page 10 of 24

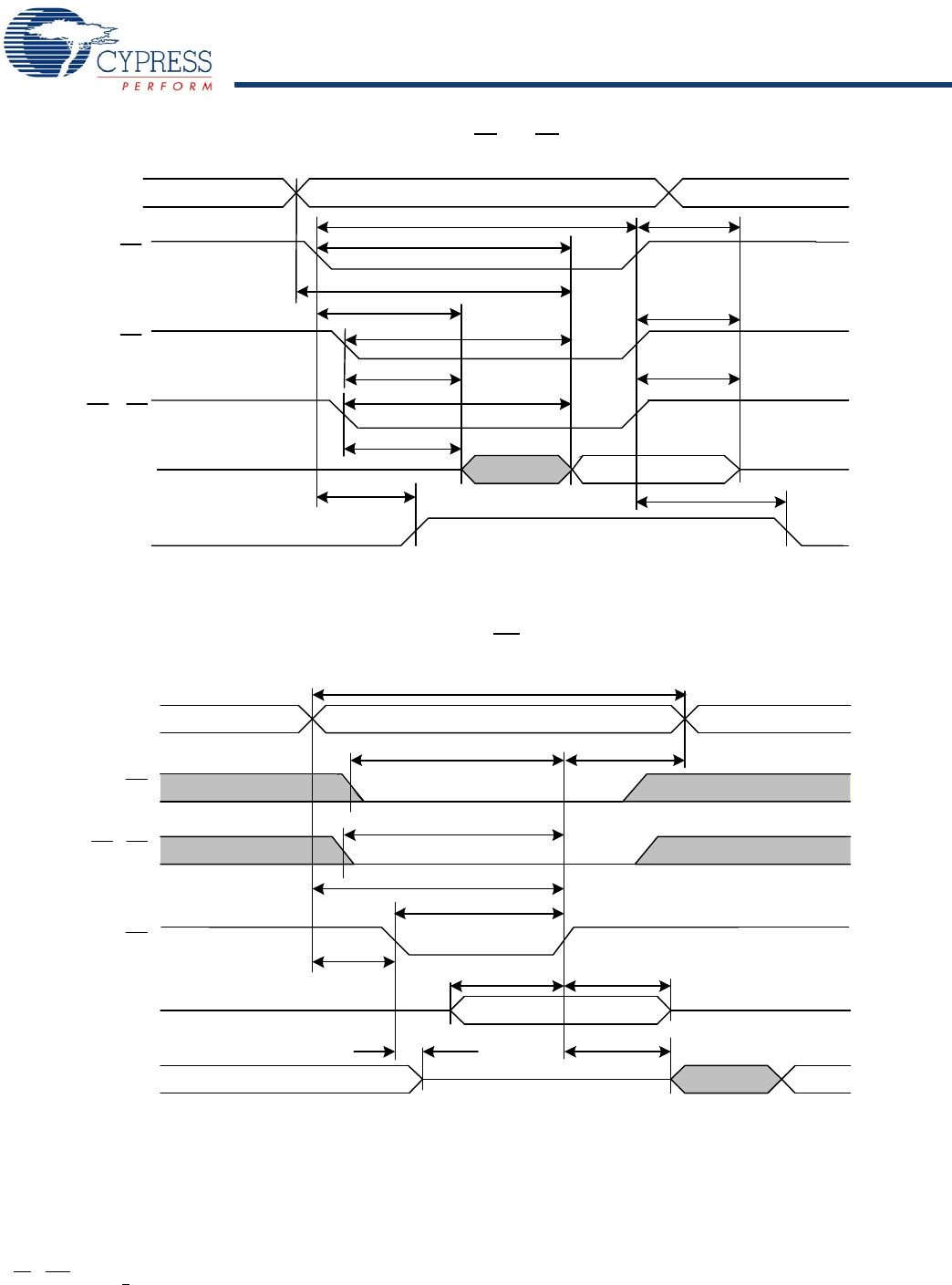

Figure 7. SRAM Read Cycle #2: CE

and OE Controlled

[3, 15, 19]

Figure 8. SRAM Write Cycle #1: WE Controlled

[3, 18, 19, 20]

$GGUHVV9DOLG$GGUHVV

'DWD2XWSXW

2XWSXW'DWD9DOLG

6WDQGE\

$FWLYH

+LJK,PSHGDQFH

&(

2(

%+(%/(

,

&&

W

+=&(

W

5&

W

$&(

W

$$

W

/=&(

W

'2(

W

/=2(

W

'%(

W

/=%(

W

38

W

3'

W

+=%(

W

+=2(

'DWD2XWSXW

'DWD,QSXW

,QSXW'DWD9DOLG

+LJK,PSHGDQFH

$GGUHVV9DOLG$GGUHVV

3UHYLRXV'DWD

W

:&

W

6&(

W

+$

W

%:

W

$:

W

3:(

W

6$

W

6'

W

+'

W

+=:(

W

/=:(

:(

%+(%/(

&(

Notes

20.CE

or WE must be >V

IH

during address transitions.

[+] Feedback