CY62137FV30 MoBL

®

Document Number: 001-07141 Rev. *F Page 5 of 12

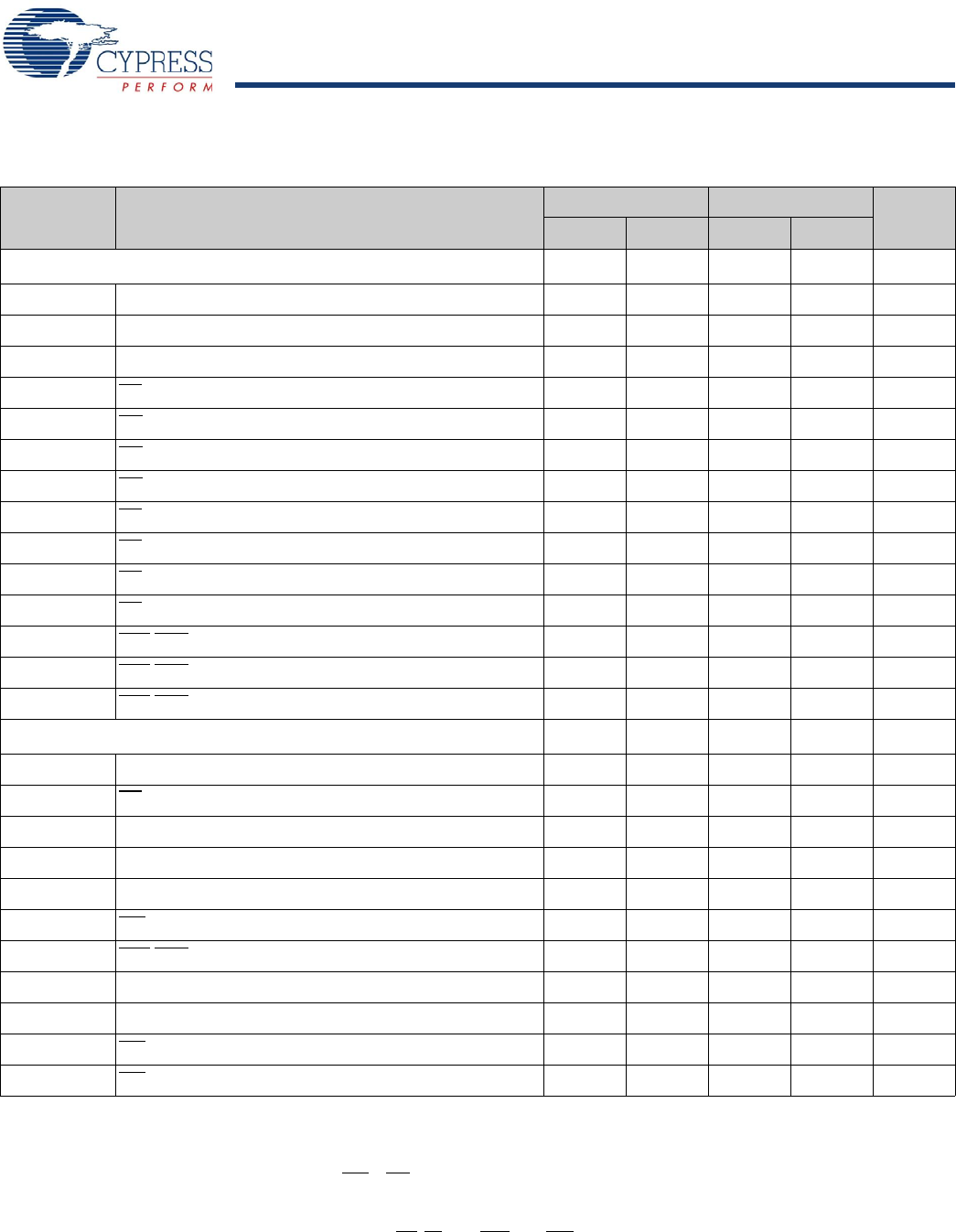

Switching Characteristics

Over the Operating Range

[11, 12]

Parameter Description

45 ns (Ind’l/Auto-A) 55 ns (Auto-E)

Unit

Min Max Min Max

Read Cycle

t

RC

Read Cycle Time 45 55 ns

t

AA

Address to Data Valid 45 55 ns

t

OHA

Data Hold From Address Change 10 10 ns

t

ACE

CE LOW to Data Valid

45 55 ns

t

DOE

OE LOW to Data Valid

22 25 ns

t

LZOE

OE LOW to Low Z

[13]

55ns

t

HZOE

OE HIGH to High Z

[13, 14]

18 20 ns

t

LZCE

CE LOW to Low Z

[13]

10 10 ns

t

HZCE

CE HIGH to High Z

[13, 14]

18 20 ns

t

PU

CE LOW to Power Up

00ns

t

PD

CE HIGH to Power Down

45 55 ns

t

DBE

BLE/BHE LOW to Data Valid

45 55 ns

t

LZBE

BLE/BHE LOW to Low Z

[13, 15]

510ns

t

HZBE

BLE/BHE HIGH to High Z

[13, 14]

18 20 ns

Write Cycle

[16]

t

WC

Write Cycle Time 45 55 ns

t

SCE

CE LOW to Write End

35 40 ns

t

AW

Address Setup to Write End 35 40 ns

t

HA

Address Hold from Write End 0 0 ns

t

SA

Address Setup to Write Start 0 0 ns

t

PWE

WE Pulse Width

35 40 ns

t

BW

BLE/BHE LOW to Write End

35 40 ns

t

SD

Data Setup to Write End 25 25 ns

t

HD

Data Hold From Write End 0 0 ns

t

HZWE

WE LOW to High Z

[13, 14]

18 20 ns

t

LZWE

WE HIGH to Low Z

[13]

10 10 ns

Notes

11. Test conditions for all parameters, other than tri-state parameters, assume signal transition time of 3 ns (1V/ns) or less, timing reference levels of V

CC(typ)

/2, input pulse

levels of 0 to V

CC(typ)

, and output loading of the specified I

OL

/I

OH

as shown in “AC Test Loads and Waveforms” on page 4.

12.AC timing parameters are subject to byte enable signals (BHE

or BLE) not switching when chip is disabled. Please see application note AN13842 for further clarification.

13.At any temperature and voltage condition, t

HZCE

is less than t

LZCE

, t

HZBE

is less than t

LZBE

, t

HZOE

is less than t

LZOE

, and t

HZWE

is less than t

LZWE

for any device.

14.t

HZOE

, t

HZCE

, t

HZBE

, and t

HZWE

transitions are measured when the outputs enter a high impedance state.

15.If both byte enables are toggled together, this value is 10 ns.

16.The internal write time of the memory is defined by the overlap of WE

, CE

= V

IL

, BHE and/or BLE = V

IL

. All signals are ACTIVE to initiate a write and any of these

signals terminate a write by going INACTIVE. The data input setup and hold timing are referenced to the edge of the signal that terminates the write.

[+] Feedback [+] Feedback