CY7C0837AV, CY7C0830AV

CY7C0831AV, CY7C0832AV

CY7C0832BV, CY7C0833AV

Document #: 38-06059 Rev. *S Page 23 of 28

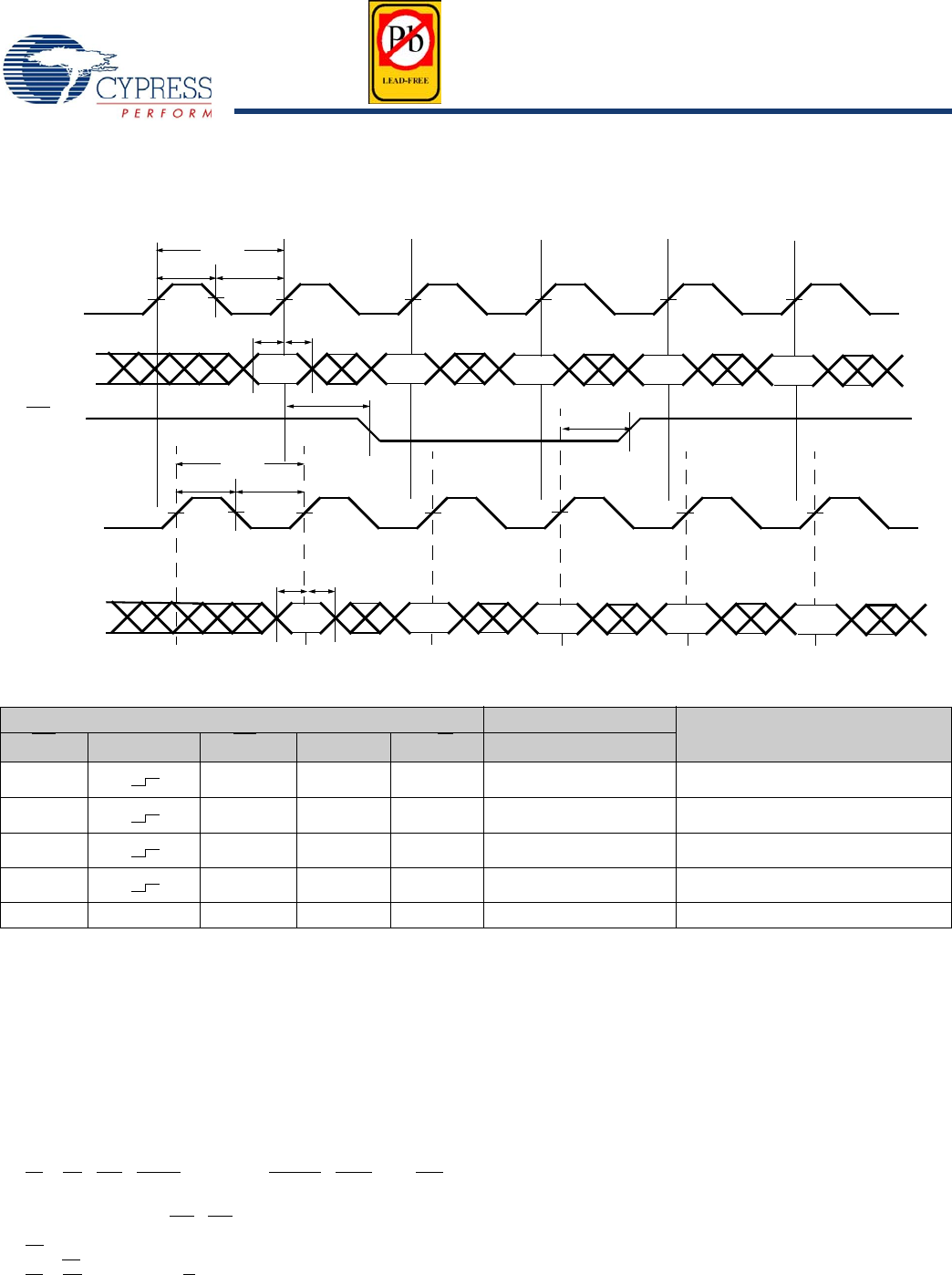

Figure 19. MailBox Interrupt Timing

[54, 55, 56, 57, 58]

Table 7. Read/Write and Enable Operation

(Any Port)

[2, 17, 59, 60, 61]

Inputs Outputs

Operation

OE CLK CE

0

CE

1

R/W DQ

0

– DQ

17

X H X X High-Z Deselected

X X L X High-Z Deselected

XLHLD

IN

Write

LLHHD

OUT

Read

H X L H X High-Z Outputs Disabled

Switching Waveforms

(continued)

t

CH2

t

CL2

t

CYC2

CLK

L

t

CH2

t

CL2

t

CYC2

CLK

R

7FFFF

t

SA

t

HA

A

n+3

A

n

A

n+1

A

n+2

L_PORT

ADDRESS

A

m

A

m+4

A

m+1

7FFFF

A

m+3

R_PORT

ADDRESS

INT

R

t

SA

t

HA

t

SINT

t

RINT

Notes

54.CE

0

= OE = ADS = CNTEN = LOW; CE

1

= CNTRST = MRST = CNT/MSK = HIGH.

55.Address “7FFFF” is the mailbox location for R_Port of the 9Mb device.

56.L_Port is configured for Write operation, and R_Port is configured for Read operation.

57.At least one byte enable (BE0

– BE1) is required to be active during interrupt operations.

58.Interrupt flag is set with respect to the rising edge of the Write clock, and is reset with respect to the rising edge of the Read clock.

59.OE

is an asynchronous input signal.

60.When CE

changes state, deselection and Read happen after one cycle of latency.

61.CE

0

= OE = LOW; CE

1

= R/W = HIGH.

[+] Feedback