CY7C1062DV33

Document Number: 38-05477 Rev.*E Page 7 of 12

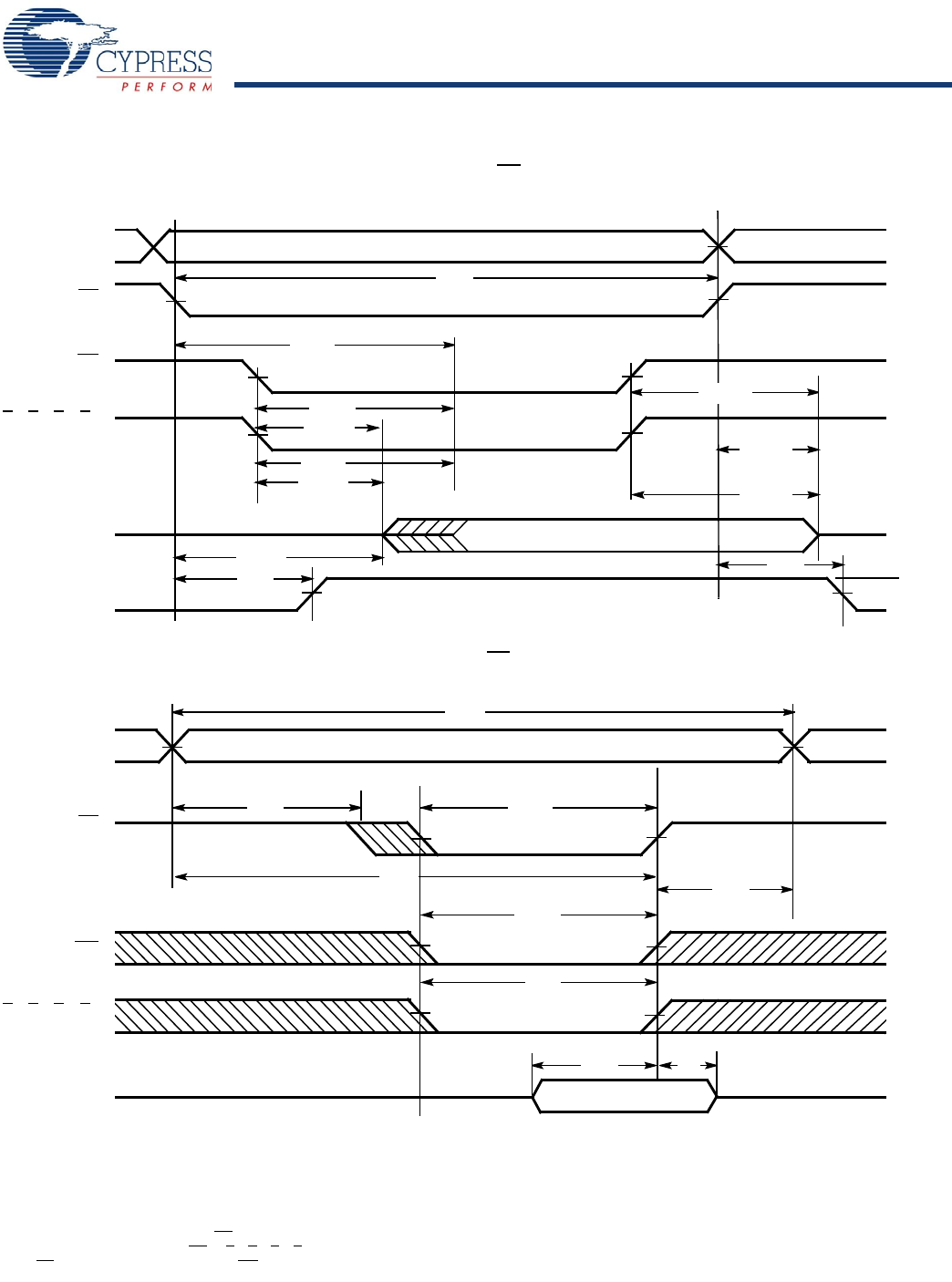

Figure 3. Read Cycle No. 2 (OE Controlled)

[3, 14, 15]

Figure 4. Write Cycle No. 1 (CE Controlled)

[3, 15, 16, 17]

Switching Waveforms (continued)

50%

50%

DATA VALID

t

RC

t

ACE

t

DOE

t

LZOE

t

LZCE

t

PU

HIGH IMPEDANCE

t

HZOE

t

HZBE

t

PD

t

DBE

t

LZBE

t

HZCE

OE

CE

ADDRESS

DATA OUT

V

CC

SUPPLY

B

A

, B

B

, B

C

, B

D

CURRENT

HIGH

IMPEDANCE

I

CC

I

SB

t

HD

t

SD

t

SCE

t

SA

t

HA

t

AW

t

PWE

t

WC

BW

t

DATA IO

ADDRESS

CE

WE

B

A

, B

B

, B

C

, B

D

Notes

15.Address valid before or similar to CE

transition LOW.

16.Data IO is high impedance if OE

or B

A

, B

B

, B

C

, B

D

= V

IH

.

17.If CE

goes HIGH simultaneously with WE going HIGH, the output remains in a high impedance state.

[+] Feedback [+] Feedback