CY7C1246V18, CY7C1257V18

CY7C1248V18, CY7C1250V18

Document Number: 001-06348 Rev. *D Page 16 of 27

TAP AC Switching Characteristics

Over the Operating Range

[13, 14]

Parameter Description Min Max Unit

t

TCYC

TCK Clock Cycle Time 50 ns

t

TF

TCK Clock Frequency 20 MHz

t

TH

TCK Clock HIGH 20 ns

t

TL

TCK Clock LOW 20 ns

Setup Times

t

TMSS

TMS Setup to TCK Clock Rise 5 ns

t

TDIS

TDI Setup to TCK Clock Rise 5 ns

t

CS

Capture Setup to TCK Rise 5 ns

Hold Times

t

TMSH

TMS Hold after TCK Clock Rise 5 ns

t

TDIH

TDI Hold after Clock Rise 5 ns

t

CH

Capture Hold after Clock Rise 5 ns

Output Times

t

TDOV

TCK Clock LOW to TDO Valid 10 ns

t

TDOX

TCK Clock LOW to TDO Invalid 0 ns

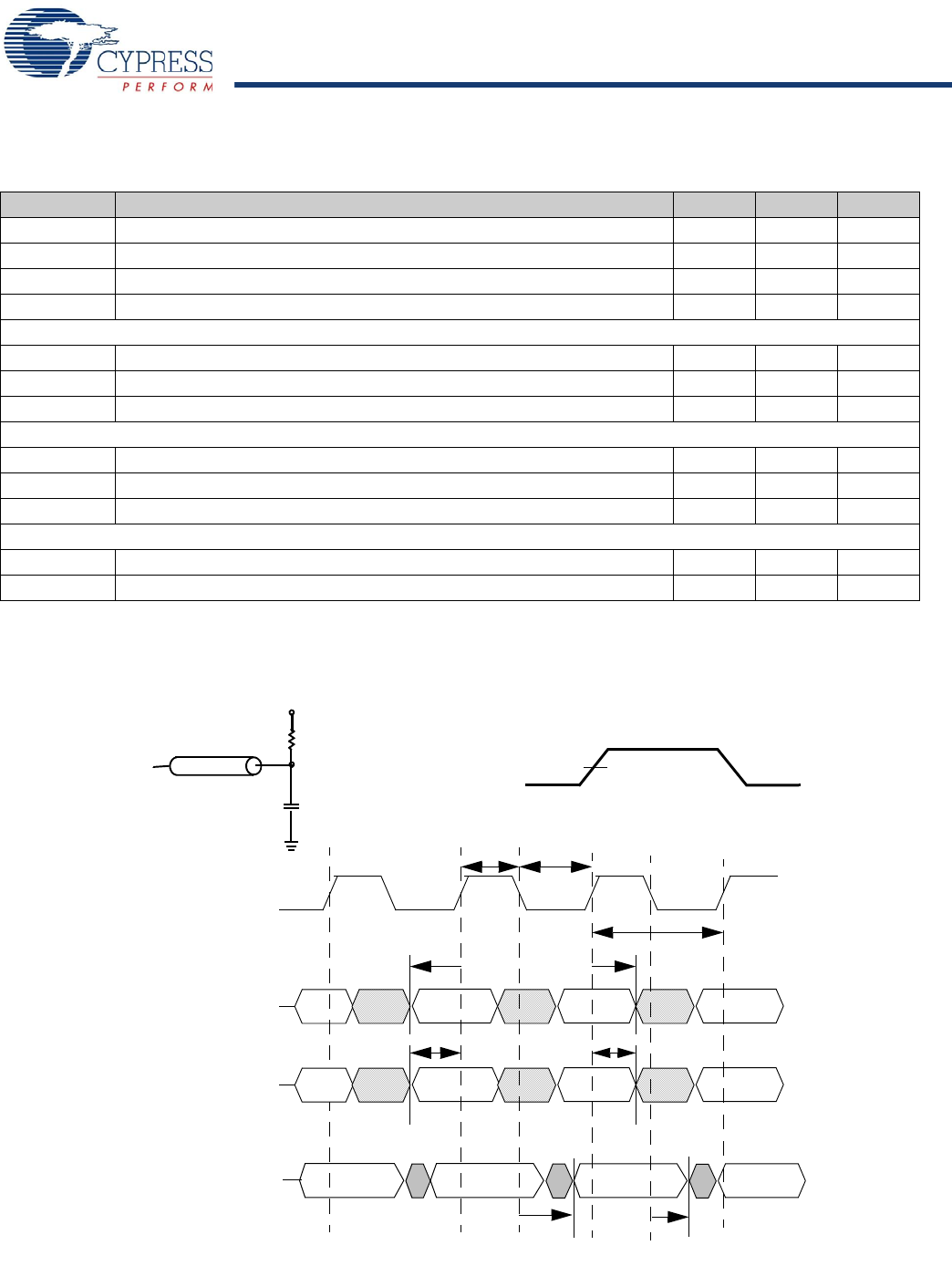

TAP Timing and Test Conditions

Figure 2

shows the TAP timing and test conditions.

[14]

Figure 2. TAP Timing and Test Conditions

t

TL

t

TH

(a)

TDO

C

L

= 20 pF

Z

0

= 50Ω

GND

0.9V

50Ω

1.8V

0V

ALL INPUT PULSES

0.9V

Test Clock

Test Mode Select

TCK

TMS

Test Data In

TDI

Test Data Out

t

TCYC

t

TMSH

t

TMSS

t

TDIS

t

TDIH

t

TDOV

t

TDOX

TDO

Notes

13.t

CS

and t

CH

refer to the setup and hold time requirements of latching data from the boundary scan register.

14.Test conditions are specified using the load in TAP AC Test Conditions. t

R

/t

F

= 1 ns.

[+] Feedback [+] Feedback