2-Mbit (128K x 18) Flow-Through Sync SRAM

CY7C1324H

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document #: 001-00208 Rev. *B Revised April 26, 2006

Features

• 128K x 18 common I/O

• 3.3V core power supply

• 3.3V/2.5V I/O supply

• Fast clock-to-output times

— 6.5 ns (133-MHz version)

• Provide high-performance 2-1-1-1 access rate

• User-selectable burst counter supporting Intel

®

Pentium

®

interleaved or linear burst sequences

• Separate processor and controller address strobes

• Synchronous self-timed write

• Asynchronous output enable

• Offered in JEDEC-standard lead-free 100-pin TQFP

package

• “ZZ” Sleep Mode option

Functional Description

[1]

The CY7C1324H is a 128K x 18 synchronous cache RAM

designed to interface with high-speed microprocessors with

minimum glue logic. Maximum access delay from clock rise is

6.5 ns (133-MHz version). A 2-bit on-chip counter captures the

first address in a burst and increments the address automati-

cally for the rest of the burst access. All synchronous inputs

are gated by registers controlled by a positive-edge-triggered

Clock Input (CLK). The synchronous inputs include all

addresses, all data inputs, address-pipelining Chip Enable

(CE

1

), depth-expansion Chip Enables (CE

2

and

CE

3

), Burst

Control inputs (ADSC

, ADSP,

and

ADV), Write Enables

(BW

[A:B]

,

and

BWE

), and Global Write (

GW

). Asynchronous

i

nputs include the Output Enable

(OE)

and the ZZ pin

. The

CY7C1324H allows either interleaved or linear burst

sequences, selected by the MODE input pin. A HIGH selects

an interleaved burst sequence, while a LOW selects a linear

burst sequence. Burst accesses can be initiated with the

Processor Address Strobe (ADSP

) or the cache Controller

Address Strobe (ADSC

) inputs. Address advancement is

controlled by the Address Advancement (ADV

) input.

Addresses and chip enables are registered at rising edge of

clock when either Address Strobe Processor (ADSP

) or

Address Strobe Controller (ADSC

) are active. Subsequent

burst addresses can be internally generated as controlled by

the Advance pin (ADV

).

The CY7C1324H operates from a +3.3V core power supply

while all outputs may operate with either a +3.3V or +2.5V

supply. All inputs and outputs are JEDEC-standard

JESD8-5-compatible.

Note:

1. For best-practices recommendations, please refer to the Cypress application note System Design Guidelines on www.cypress.com.

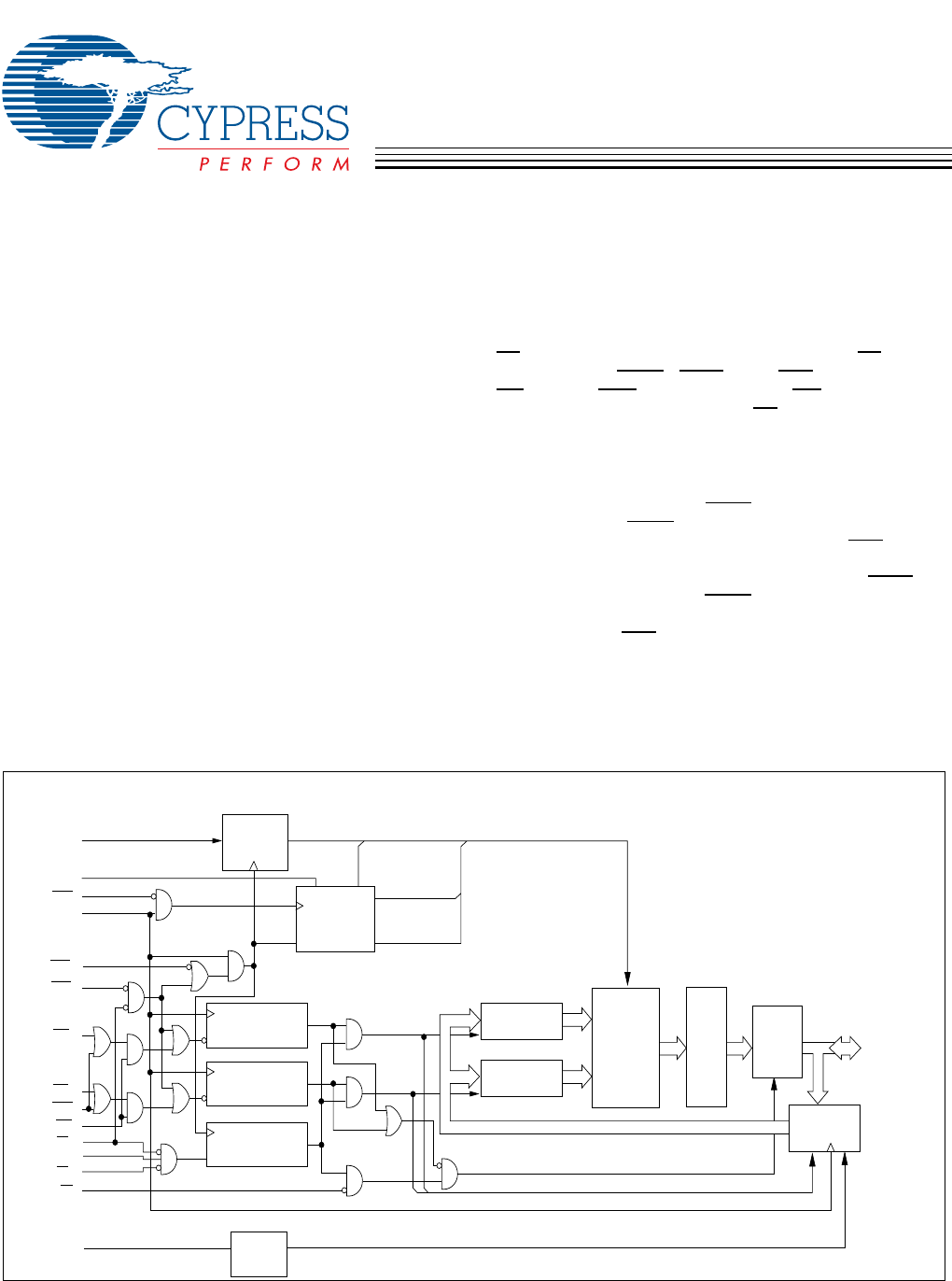

ADDRESS

REGISTER

ADV

CLK

BURST

COUNTER AND

LOGIC

CLR

Q1

Q0

ADSC

CE

1

OE

SENSE

AMPS

MEMORY

ARRAY

ADSP

OUTPUT

BUFFERS

INPUT

REGISTERS

MODE

CE

2

CE

3

GW

BWE

A

0,A1,A

BW

B

BW

A

DQ

B

,DQP

B

WRITE REGISTER

DQ

A

,DQP

A

WRITE REGISTER

ENABLE

REGISTER

A[1:0]

DQs

DQP

A

DQP

B

DQ

B

,DQP

B

WRITE DRIVER

DQ

A

,DQP

A

WRITE DRIVER

SLEEP

CONTROL

ZZ

Logic Block Diagram

[+] Feedback