CY7C1371D

CY7C1373D

Document #: 38-05556 Rev. *F Page 16 of 29

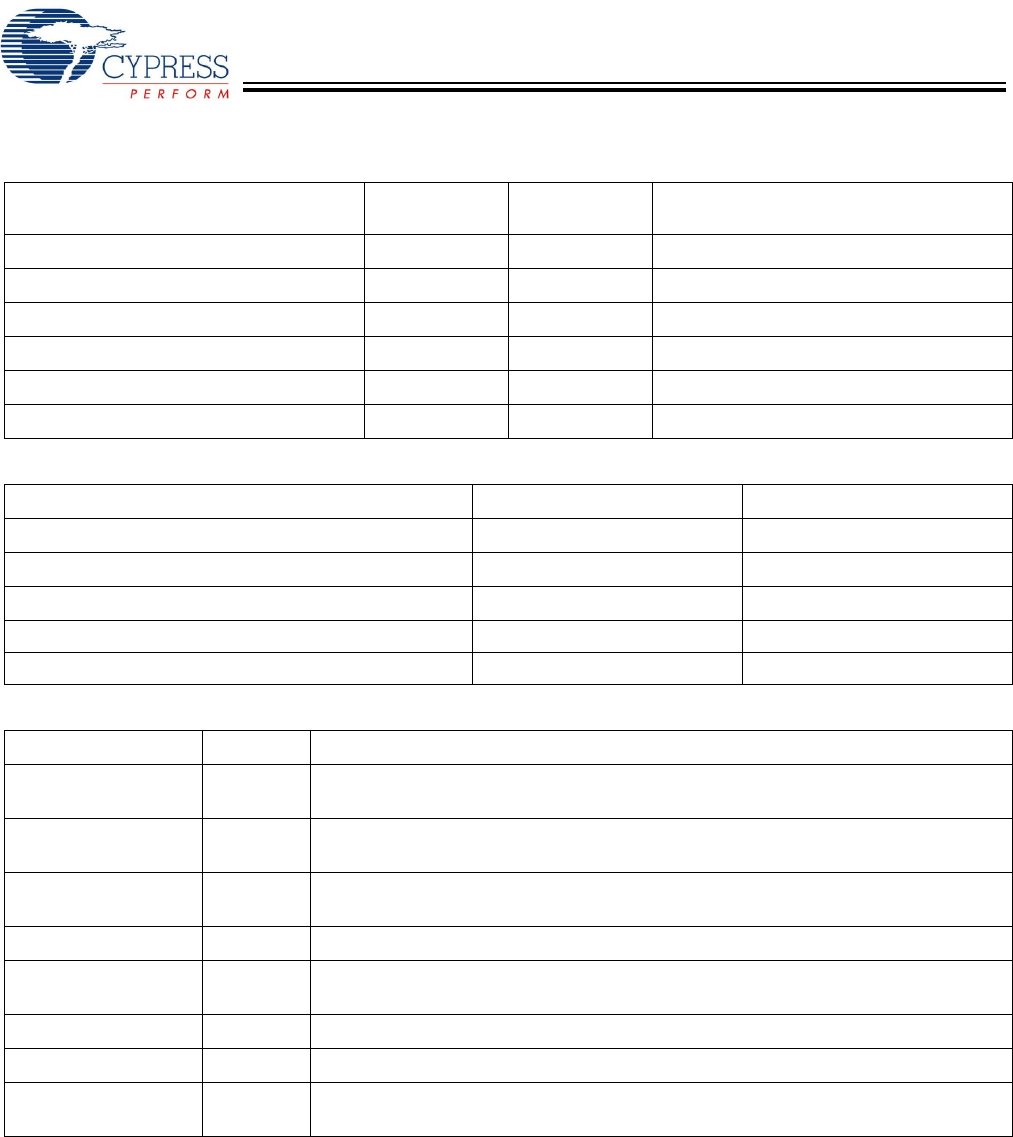

Identification Register Definitions

Instruction Field

CY7C1371D

(512K X 36)

CY7C1373D

(1M X 18) Description

Revision Number (31:29) 000 000 Describes the version number

Device Depth (28:24) 01011 01011 Reserved for internal use

Device Width (23:18) 001001 001001 Defines memory type and architecture

Cypress Device ID (17:12) 100101 010101 Defines width and density

Cypress JEDEC ID Code (11:1) 00000110100 00000110100 Allows unique identification of SRAM vendor

ID Register Presence Indicator (0) 1 1 Indicates the presence of an ID register

Scan Register Sizes

Register Name Bit Size (x36) Bit Size (x18)

Instruction 3 3

Bypass 1 1

ID 32 32

Boundary Scan Order (119-Ball BGA package) 85 85

Boundary Scan Order (165-Ball FBGA package) 89 89

Identification Codes

Instruction Code Description

EXTEST 000 Captures IO ring contents. Places the boundary scan register between TDI and TDO.

Forces all SRAM outputs to High-Z state.

IDCODE 001 Loads the ID register with the vendor ID code and places the register between TDI and

TDO. This operation does not affect SRAM operations.

SAMPLE Z 010 Captures IO ring contents. Places the boundary scan register between TDI and TDO.

Forces all SRAM output drivers to a High-Z state.

RESERVED 011 Do Not Use: This instruction is reserved for future use.

SAMPLE/PRELOAD 100 Captures IO ring contents. Places the boundary scan register between TDI and TDO.

Does not affect SRAM operation.

RESERVED 101 Do Not Use: This instruction is reserved for future use.

RESERVED 110 Do Not Use: This instruction is reserved for future use.

BYPASS 111 Places the bypass register between TDI and TDO. This operation does not affect SRAM

operations.

[+] Feedback