CY7C1370DV25

CY7C1372DV25

Document #: 38-05558 Rev. *D Page 17 of 27

Maximum Ratings

(Above which the useful life may be impaired. For user guide-

lines, not tested.)

Storage Temperature .................................–65°C to +150°C

Ambient Temperature with

Power Applied.............................................–55°C to +125°C

Supply Voltage on V

DD

Relative to GND........ –0.5V to +3.6V

Supply Voltage on V

DDQ

Relative to GND ......–0.5V to +V

DD

DC to Outputs in Tri-State................... –0.5V to V

DDQ

+ 0.5V

DC Input Voltage ...................................–0.5V to V

DD

+ 0.5V

Current into Outputs (LOW).........................................20 mA

Static Discharge Voltage.......................................... > 2001V

(per MIL-STD-883, Method 3015)

Latch-up Current.................................................... > 200 mA

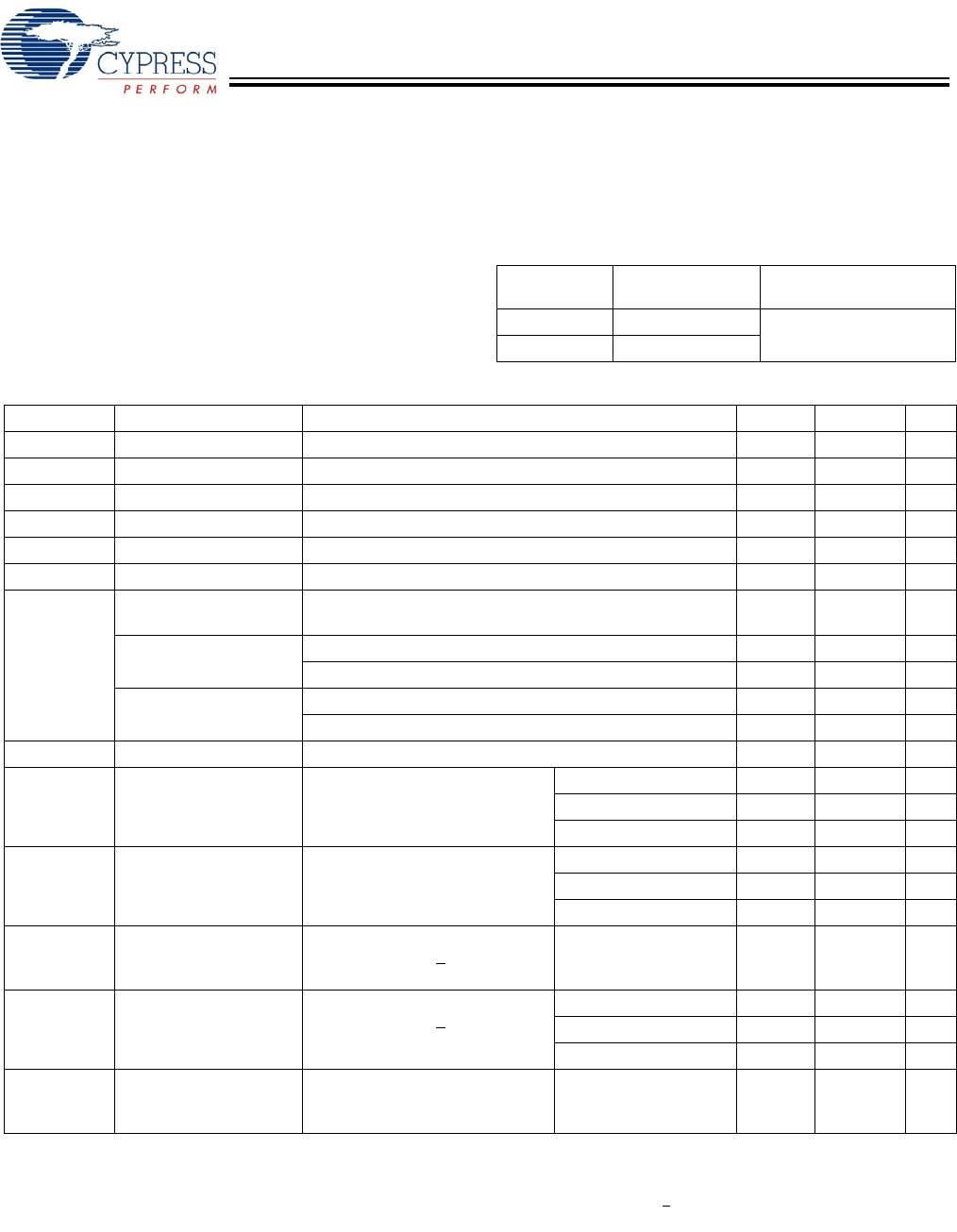

Operating Range

Range

Ambient

Temperature

V

DD

/V

DDQ

Commercial 0°C to +70°C 2.5V ±5%

Industrial –40°C to +85°C

Electrical Characteristics Over the Operating Range

[15, 16]

Parameter Description Test Conditions Min. Max. Unit

V

DD

Power Supply Voltage 2.375 2.625 V

V

DDQ

I/O Supply Voltage for 2.5V I/O 2.375 V

DD

V

V

OH

Output HIGH Voltage for 2.5V I/O, I

OH

= −1.0 mA 2.0 V

V

OL

Output LOW Voltage for 2.5V I/O, I

OL

= 1.0 mA 0.4 V

V

IH

Input HIGH Voltage

[17]

for 2.5V I/O 1.7 V

DD

+ 0.3V V

V

IL

Input LOW Voltage

[17]

for 2.5V I/O –0.3 0.7 V

I

X

Input Leakage Current

except ZZ and MODE

GND ≤ V

I

≤ V

DDQ

–5 5 µA

Input Current of MODE Input = V

SS

–30 µA

Input = V

DD

5 µA

Input Current of ZZ Input = V

SS

–5 µA

Input = V

DD

30 µA

I

OZ

Output Leakage Current GND ≤ V

I

≤ V

DD,

Output Disabled –5 5 µA

I

DD

V

DD

Operating Supply V

DD

= Max., I

OUT

= 0 mA,

f = f

MAX

= 1/t

CYC

4.0-ns cycle, 250 MHz 350 mA

5.0-ns cycle, 200 MHz 300 mA

6.0-ns cycle, 167 MHz 275 mA

I

SB1

Automatic CE

Power-down

Current—TTL Inputs

Max. V

DD

, Device Deselected,

V

IN

≥ V

IH

or V

IN

≤ V

IL

, f = f

MAX

=

1/t

CYC

4.0-ns cycle, 250 MHz 160 mA

5.0-ns cycle, 200 MHz 150 mA

6.0-ns cycle, 167 MHz 140 mA

I

SB2

Automatic CE

Power-down

Current—CMOS Inputs

Max. V

DD

, Device Deselected,

V

IN

≤ 0.3V or V

IN

> V

DDQ

− 0.3V,

f = 0

All speed grades 70 mA

I

SB3

Automatic CE

Power-down

Current—CMOS Inputs

Max. V

DD

, Device Deselected,

V

IN

≤ 0.3V or V

IN

> V

DDQ

− 0.3V,

f = f

MAX

= 1/t

CYC

4.0-ns cycle, 250 MHz 135 mA

5.0-ns cycle, 200 MHz 130 mA

6.0-ns cycle, 167 MHz 125 mA

I

SB4

Automatic CE

Power-down

Current—TTL Inputs

Max. V

DD

, Device Deselected,

V

IN

≥ V

IH

or V

IN

≤ V

IL

, f = 0

All speed grades 80 mA

Notes:

15.Overshoot: V

IH

(AC) < V

DD

+1.5V (Pulse width less than t

CYC

/2), undershoot: V

IL

(AC)> –2V (Pulse width less than t

CYC

/2).

16.T

Power-up

: Assumes a linear ramp from 0V to V

DD

(min.) within 200 ms. During this time V

IH

< V

DD

and V

DDQ

< V

DD

.

17.Tested initially and after any design or process change that may affect these parameters.

[+] Feedback