CY7C1460AV33

CY7C1462AV33

CY7C1464AV33

Document #: 38-05353 Rev. *D Page 2 of 27

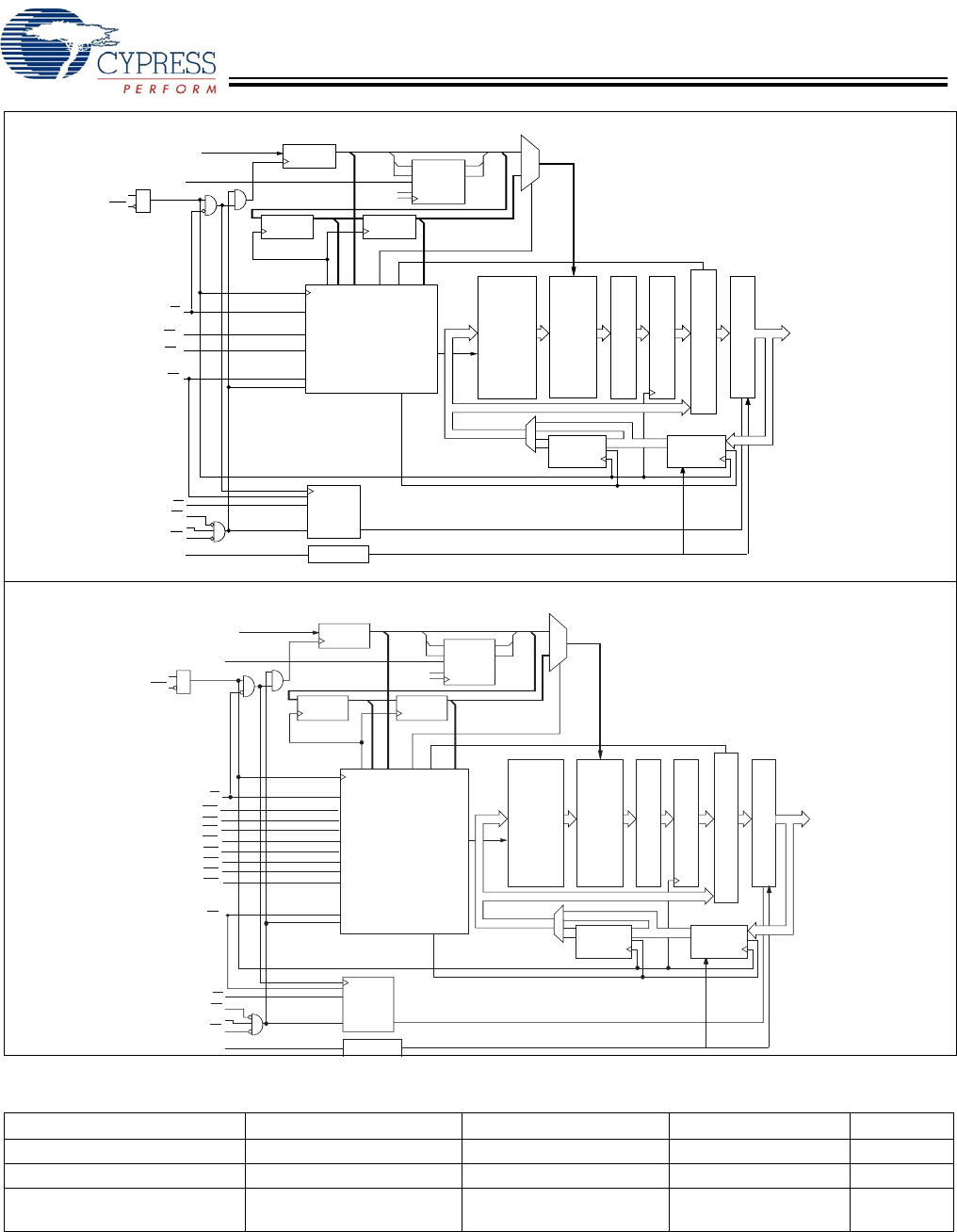

A0, A1, A

C

MODE

BW

a

BW

b

WE

CE1

CE2

CE3

OE

READ LOGIC

DQs

DQP

a

DQP

b

D

A

T

A

S

T

E

E

R

I

N

G

O

U

T

P

U

T

B

U

F

F

E

R

S

MEMORY

ARRAY

E

E

INPUT

REGISTER 0

ADDRESS

REGISTER 0

WRITE ADDRESS

REGISTER 1

WRITE ADDRESS

REGISTER 2

WRITE REGISTRY

AND DATA COHERENCY

CONTROL LOGIC

BURST

LOGIC

A0'

A1'

D1

D0

Q1

Q0

A0

A1

C

ADV/LD

ADV/LD

E

INPUT

REGISTER 1

S

E

N

S

E

A

M

P

S

O

U

T

P

U

T

R

E

G

I

S

T

E

R

S

E

C

LK

C

EN

WRITE

DRIVERS

ZZ

Sleep

Control

Logic Block Diagram-CY7C1462AV33 (2M x 18)

A0, A1, A

C

MODE

CE1

CE2

CE3

OE

READ LOGIC

DQ

s

DQ

P

a

DQ

P

b

DQ

P

c

DQ

P

d

DQ

P

e

DQ

P

f

DQ

P

g

DQ

P

h

D

A

T

A

S

T

E

E

R

I

N

G

O

U

T

P

U

T

B

U

F

F

E

R

S

MEMORY

ARRAY

E

E

INPUT

REGISTER 0

ADDRESS

REGISTER 0

WRITE ADDRESS

REGISTER 1

WRITE ADDRESS

REGISTER 2

BURST

LOGIC

A0'

A1'

D1

D0

Q1

Q0

A0

A1

C

ADV/LD

ADV/LD

E

INPUT

REGISTER 1

S

E

N

S

E

A

M

P

S

O

U

T

P

U

T

R

E

G

I

S

T

E

R

S

E

C

LK

C

EN

WRITE

DRIVERS

BW

a

BW

b

WE

ZZ

Sleep

Control

BW

c

WRITE REGISTRY

AND DATA COHERENCY

CONTROL LOGIC

BW

d

BW

e

BW

f

BW

g

BW

h

Logic Block Diagram-CY7C1464AV33 (512K x 72)

Selection Guide

250 MHz 200 MHz 167 MHz Unit

Maximum Access Time 2.6 3.2 3.4 ns

Maximum Operating Current 475 425 375 mA

Maximum CMOS Standby

Current

120 120 120 mA

[+] Feedback