CY7C1460AV33

CY7C1462AV33

CY7C1464AV33

Document #: 38-05353 Rev. *D Page 5 of 27

Pin Definitions

Pin Name I/O Type Pin Description

A0

A1

A

Input-

Synchronous

Address Inputs used to select one of the address locations. Sampled at the rising

edge of the CLK.

BW

a

BW

b

BW

c

BW

d

BW

e

BW

f

BW

g

BW

h

Input-

Synchronous

Byte Write Select Inputs, active LOW. Qualified with WE to conduct writes to the SRAM.

Sampled on the rising edge of CLK. BW

a

controls DQ

a

and DQP

a

, BW

b

controls DQ

b

and

DQP

b

, BW

c

controls DQ

c

and DQP

c

, BW

d

controls DQ

d

and DQP

d

, BW

e

controls DQ

e

and

DQP

e

, BW

f

controls DQ

f

and DQP

f

, BW

g

controls DQ

g

and DQP

g

, BW

h

controls DQ

h

and

DQP

h

.

WE Input-

Synchronous

Write Enable Input, active LOW. Sampled on the rising edge of CLK if CEN is active

LOW. This signal must be asserted LOW to initiate a write sequence.

ADV/LD

Input-

Synchronous

Advance/Load Input used to advance the on-chip address counter or load a new

address. When HIGH (and CEN

is asserted LOW) the internal burst counter is advanced.

When LOW, a new address can be loaded into the device for an access. After being

deselected, ADV/LD should be driven LOW in order to load a new address.

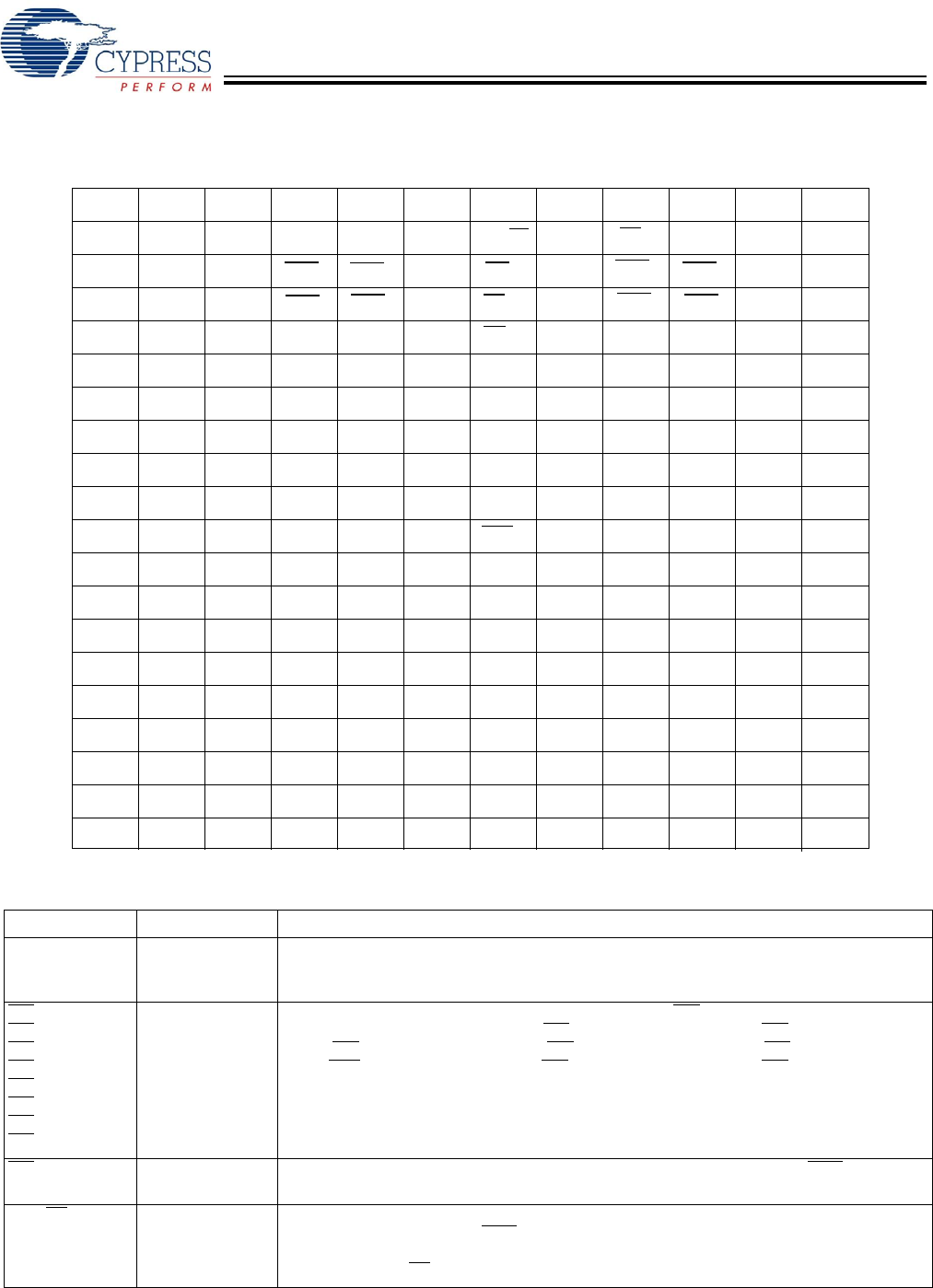

Pin Configurations (continued)

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

123456789 1110

DQg

DQg

DQg

DQg

DQg

DQg

DQg

DQg

DQc

DQc

DQc

DQc

NC

DQPg

DQh

DQh

DQh

DQh

DQd

DQd

DQd

DQd

DQPd

DQPc

DQc

DQc

DQc

DQc

NC

DQh

DQh

DQh

DQh

DQPh

DQd

DQd

DQd

DQd

DQb

DQb

DQb

DQb

DQb

DQb

DQb

DQb

DQf

DQf

DQf

DQf

NC

DQPf

DQa

DQa

DQa

DQa

DQe

DQe

DQe

DQe

DQPa

DQPb

DQf

DQf

DQf

DQf

NC

DQa

DQa

DQa

DQa

DQPe

DQe

DQe

DQe

DQe

AA AA

NC

NC

NC/144M

NC/72M A NC/288M

A

AA

AA

A

A1

A0

A

AA

AA

A

NC/576M

NC

NC

NC

NC

NC

BWS

b

BWS

f

BWS

e

BWS

a

BWS

c

BWS

g

BWS

d

BWS

h

TMS

TDI TDO TCK

NC

NC MODE

NC

CEN

V

SS

NC

CLK

NC

V

SS

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

NC/1G

V

DD

NC

OE

CE

3

CE

1

CE

2

ADV/LD

WE

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

ZZ

V

SS

V

SS

V

SS

V

SS

NC

V

DDQ

V

SS

V

SS

NC

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

NC

V

SS

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

209-ball FBGA (14 x 22 x 1.76 mm)

Pinout

CY7C1464AV33 (512K x 72)

[+] Feedback