CY7C63413C

CY7C63513C

CY7C63613C

Document #: 38-08027 Rev. *B Page 3 of 32

.

Note:

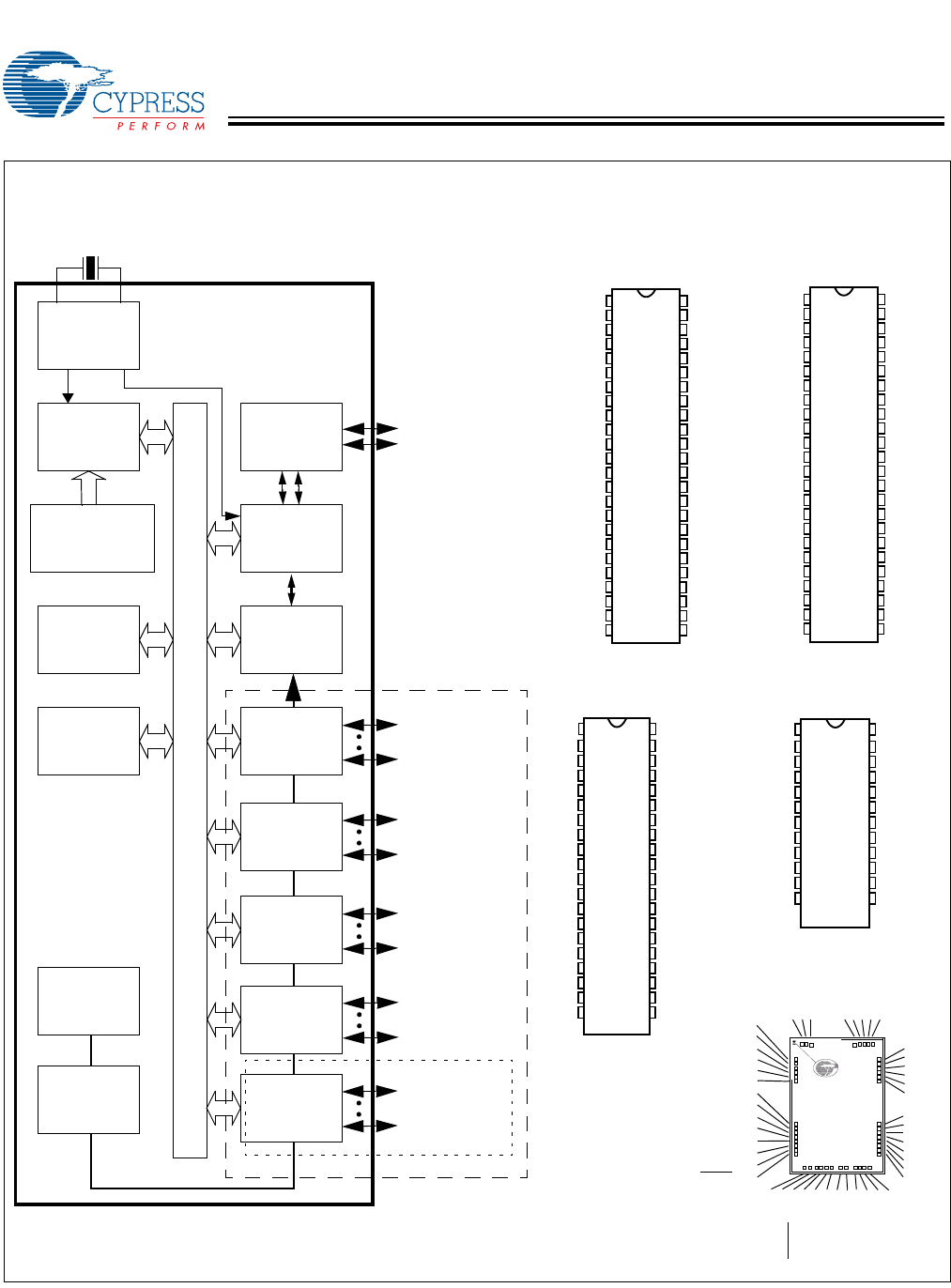

1. CY7C63613C is not bonded out for all GPIO pins shown in Logic Block Diagram. Refer to pin configuration diagram for bonded out pins. See note on page 12

for firmware code needed for unused GPIO pins.

Logic Block Diagram

Interrupt

Controller

EPROM

12-bit

Timer

Reset

Watch Dog

Timer

Power-on

GPIO

PORT 1

GPIO

PORT 0

P0[0]

P0[7]

P1[0]

P1[7]

8-bit Bus

6-MHz ceramic resonator

RAM

USB

SIE

USB

Transceiver

D+

D–

USB

GPIO

PORT 3

GPIO

PORT 2

P2[0]

P2[7]

P3[0]

P3[7]

DAC

PORT

DAC[0]

DAC[7]

High Current

Outputs

256 byte

4/6/8 Kbyte

OSC

6 MHz

12-MHz

8-bit

CPU

12 MHz

Pin Configuration

PS/2

PORT

CY7C63413C

1

2

3

4

5

6

7

9

11

12

13

14

15

16

18

17

D–

10

8

19

20

31

30

29

33

32

35

34

37

36

39

38

40

25

27

26

28

V

CC

V

SS

P3[6]

P3[4]

P3[2]

P3[0]

P2[6]

P2[4]

P3[7]

P3[5]

P3[3]

P3[1]

P2[7]

P2[5]

P2[3]

P2[1]

P1[7]

P1[5]

P1[3]

P1[1]

P0[7]

P0[5]

P0[3]

P0[1]

V

PP

Vss

D+

P2[2]

P2[0]

P1[6]

P1[4]

P1[2]

P1[0]

P0[6]

P0[4]

P0[2]

P0[0]

XTAL

OUT

XTAL

IN

40-pin PDIP

1

2

3

4

5

6

7

9

11

12

13

14

15

16

18

17

D–

10

8

19

20

31

30

29

33

32

35

34

37

36

39

38

41

40

43

42

45

44

46

48

47

21

22

23

24

25

27

26

28

V

CC

Vss

P3[6]

P3[4]

P3[2]

P3[0]

P2[6]

P2[4]

P3[7]

P3[5]

P3[3]

P3[1]

P2[7]

P2[5]

P2[3]

P2[1]

P1[7]

P1[5]

P1[3]

P1[1]

NC

NC

P0[7]

P0[5]

P0[3]

P0[1]

NC

NC

V

PP

Vss

D+

P2[2]

P2[0]

P1[6]

P1[4]

P1[2]

P1[0]

NC

NC

P0[6]

P0[4]

P0[2]

P0[0]

NC

NC

XTAL

OUT

XTAL

IN

CY7C63513C

1

2

3

4

5

6

7

9

11

12

13

14

15

16

18

17

D–

10

8

19

20

31

30

29

33

32

35

34

37

36

39

38

41

40

43

42

45

44

46

48

47

21

22

23

24

25

27

26

28

V

CC

Vss

P3[6]

P3[4]

P3[2]

P3[0]

P2[6]

P2[4]

P3[7]

P3[5]

P3[3]

P3[1]

P2[7]

P2[5]

P2[3]

P2[1]

P1[7]

P1[5]

P1[3]

P1[1]

DAC[7]

DAC[5]

P0[7]

P0[5]

P0[3]

P0[1]

DAC[3]

DAC[1]

V

PP

Vss

D+

P2[2]

P2[0]

P1[6]

P1[4]

P1[2]

P1[0]

DAC[6]

DAC[4]

P0[6]

P0[4]

P0[2]

P0[0]

DAC[2]

DAC[0]

XTAL

OUT

XTAL

IN

21

23

22

24

CY7C63413C

48-pin SSOP

48-pin SSOP

D+

D–

P3[7]

P3[3]

P3[5]

P3[1]

P2[5]

P2[3]

P2[1]

P1[7]

P1[5]

P1[3]

P1[1]

P2[7]

DAC[3]

DAC[1]

V

PP

Vss

XTAL

OUT

XTAL

IN

DAC[7]

DAC[5]

P0[7]

P0[5]

P0[3]

P0[1]

DAC[6]

DAC[4]

P0[6]

P0[4]

P0[2]

P0[0]

DAC[2]

DAC[0]

V

CC

Vss

P3[6]

P3[4]

P3[2]

P3[0]

P2[6]

P2[4]

P2[2]

P2[0]

P1[6]

P1[4]

P1[2]

P1[0]

CY7C63413C

48-Pad Die

0

0

CY7C63613C

1

2

3

4

5

6

7

9

11

12

D–

10

8

15

14

13

17

16

19

18

21

20

23

22

24

V

CC

V

SS

P3[6]

P3[4]

P1[2]

P1[0]

P0[6]

P0[4]

P3[7]

P3[5]

P1[3]

P1[1]

P0[7]

P0[5]

P0[3]

P0[1]

V

PP

Vss

D+

P0[2]

P0[0]

XTAL

OUT

XTAL

IN

24-pin SOIC

CY7C63513C only

See Note 1

.

[+] Feedback