CY7C68033/CY7C68034

Document #: 001-04247 Rev. *D Page 4 of 33

Buses

The NX2LP-Flex features an 8- or 16-bit ‘FIFO’ bidirectional

data bus, multiplexed on I/O ports B and D.

The default firmware image implements an 8-bit data bus in

GPIF Master mode. It is recommended that additional inter-

faces added to the default firmware image use this 8-bit data

bus.

Enumeration

During the start-up sequence, internal logic checks for the

presence of NAND Flash with valid firmware. If valid firmware

is found, the NX2LP-Flex loads it and operates according to

the firmware. If no NAND Flash is detected, or if no valid

firmware is found, the NX2LP-Flex uses the default values

from internal ROM space for manufacturing mode operation.

The two modes of operation are described in the section

”Normal Operation Mode” on page 5 and ”Manufacturing

Mode” on page 5.

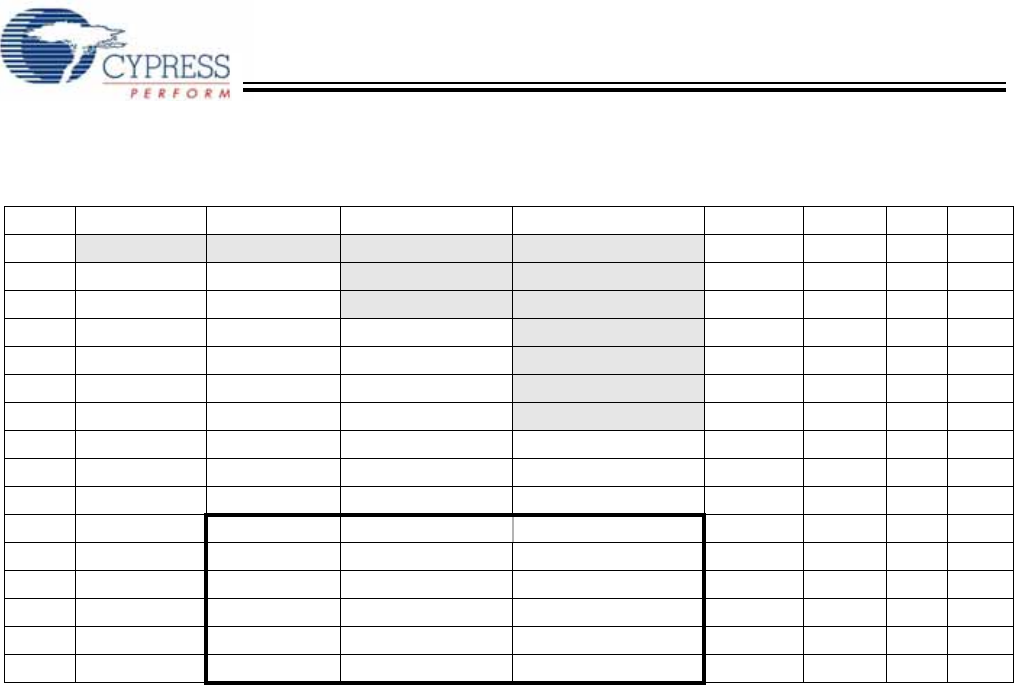

Table 1. Special Function Registers

x8x 9x Ax Bx CxDxExFx

0

IOA IOB IOC IOD SCON1 PSW ACC B

1SP EXIF INT2CLR IOE SBUF1

2DPL0 MPAGE

INT4CLR OEA

3DPH0

OEB

4 DPL1 OEC

5 DPH1

OED

6 DPS

OEE

7PCON

8 TCON SCON0 IE IP T2CON EICON EIE EIP

9 TMOD SBUF0

ATL0AUTOPTRH1 EP2468STAT EP01STAT RCAP2L

BTL1AUTOPTRL1 EP24FIFOFLGS GPIFTRIG RCAP2H

CTH0RESERVED EP68FIFOFLGS TL2

DTH1AUTOPTRH2 GPIFSGLDATH TH2

E CKCON AUTOPTRL2 GPIFSGLDATLX

F RESERVED AUTOPTRSET-UP GPIFSGLDATLNOX

[+] Feedback