CY7C68300C/CY7C68301C

CY7C68320C/CY7C68321C

Document 001-05809 Rev. *A Page 9 of 42

30 16 23 SDA IO Data signal for I

2

C interface. (See “SCL, SDA” on

page 11).

Apply a 2.2k pull up resistor.

31

32

N/A N/A NC No connect.

33 17 24 V

CC

PWR V

CC

. Connect to 3.3V power source.

34 18 25 DD0 IO

[1]

Hi-Z ATA data bit 0.

35 19 26 DD1 IO

[1]

Hi-Z ATA data bit 1.

36 20 27 DD2 IO

[1]

Hi-Z ATA data bit 2.

37 21 28 DD3 IO

[1]

Hi-Z ATA data bit 3.

38 N/A N/A V

CC

PWR V

CC

. Connect to 3.3V power source.

39 N/A N/A GND GND Ground.

40 N/A N/A NC NC No connect.

41 N/A N/A GND Ground.

42 N/A N/A NC NC No connect.

43 N/A N/A GND Ground.

44 22 29 DD4 IO

[1]

Hi-Z ATA data bit 4.

45 23 30 DD5 IO

[1]

Hi-Z ATA data bit 5.

46 24 31 DD6 IO

[1]

Hi-Z ATA data bit 6.

47 25 32 DD7 IO

[1]

Hi-Z ATA data bit 7. Apply a 1k pull down to GND.

48 26 33 GND GND Ground.

49 27 34 V

CC

PWR V

CC

. Connect to 3.3V power source.

50 28 35 GND GND Ground.

51

52

N/A N/A NC NC No connect.

53 N/A N/A V

CC

PWR V

CC

. Connect to 3.3V power source.

54 29 36 DIOW#

[2]

O/Z

[1]

Driven HIGH

(CMOS)

ATA control.

55 30 37 DIOR# O/Z

[1]

Driven HIGH

(CMOS)

ATA control.

56 31 38 DMACK# O/Z

[1]

Driven HIGH

(CMOS)

ATA control.

57 N/A N/A NC NC No connect.

58 N/A N/A LOWPWR# O USB suspend indicator. (See “LOWPWR#” on

page 13).

59

60

61

N/A N/A NC NC No connect.

62 N/A N/A VBUSPWRD I Input Bus-powered mode selector. (See “VBUSPWRD” on

page 14).

63

64

N/A N/A NC NC No connect.

65 N/A N/A GND GND Ground.

66 32 39 V

CC

PWR V

CC

. Connect to 3.3V power source.

67 33 40 INTRQ I

[1]

Input ATA interrupt request.

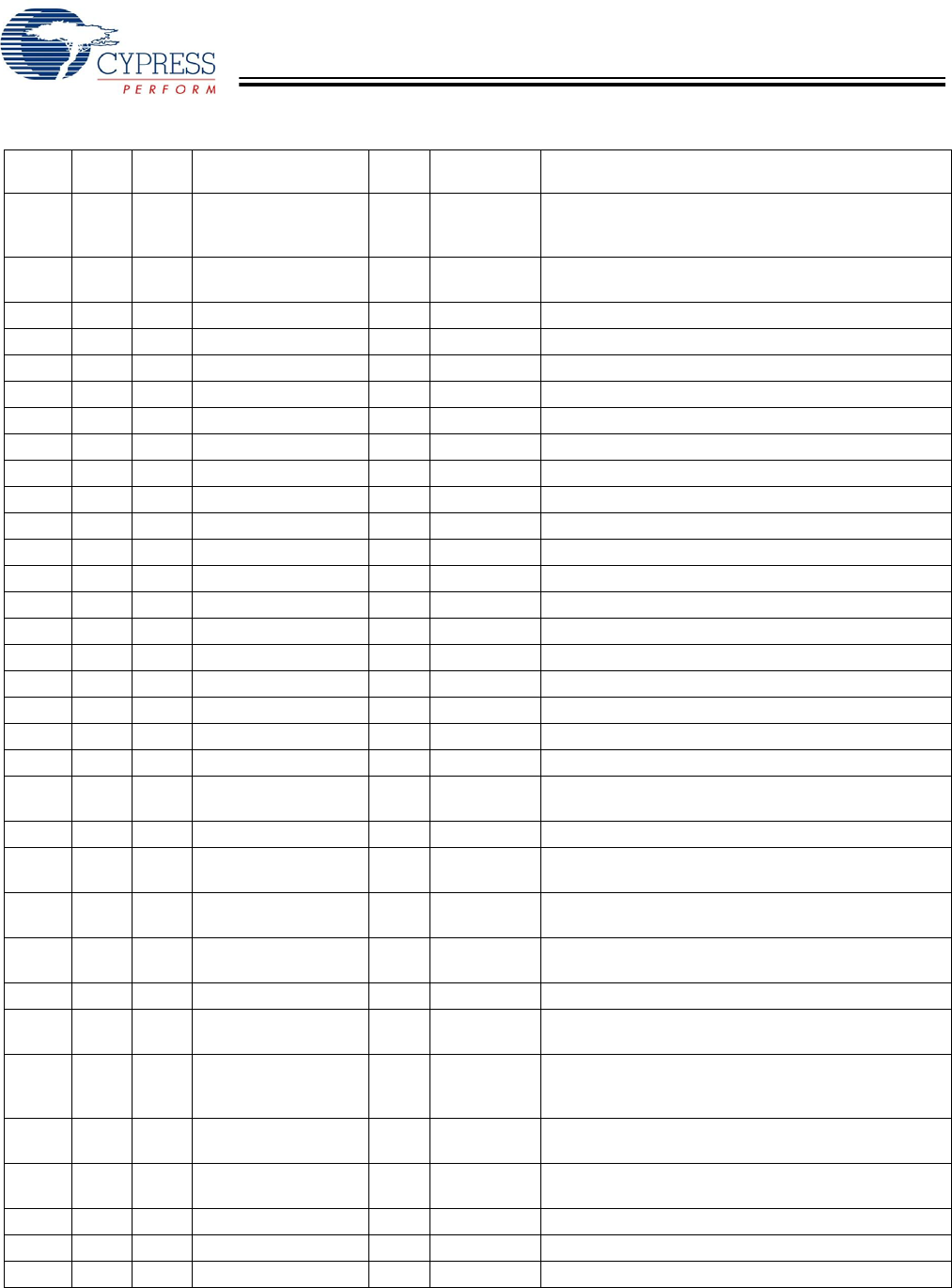

Table 1. AT2LP Pin Descriptions

Note: (Italic pin names denote pin functionality during CY7C68300A compatibility mode) (continued)

100

TQFP

56

QFN

56

SSOP

Pin Name

Pin

Type

Default State

at Startup

Pin Description

[+] Feedback