CY7C68300C/CY7C68301C

CY7C68320C/CY7C68321C

Document 001-05809 Rev. *A Page 8 of 42

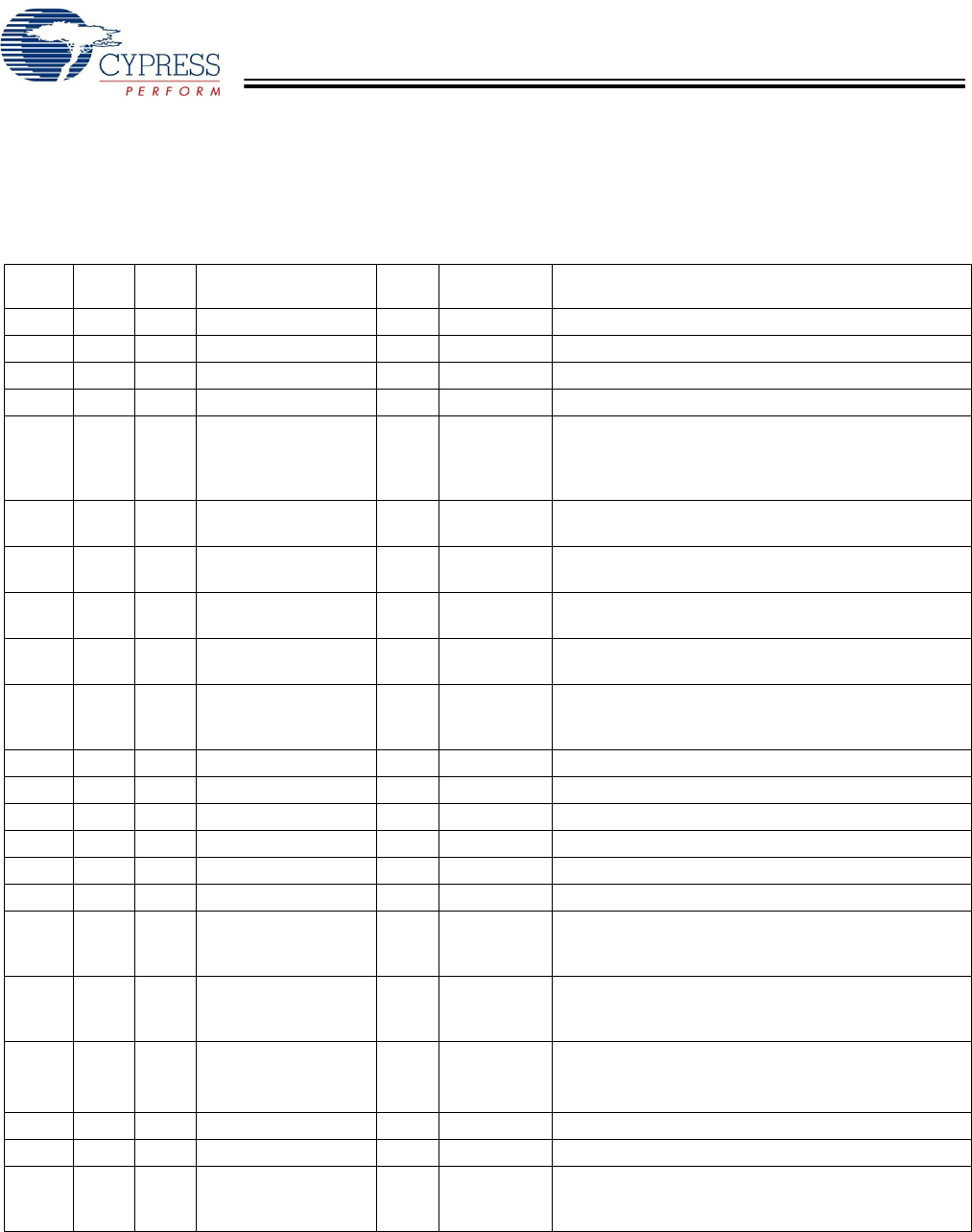

Pin Descriptions

The following table lists the pinouts for the 56-pin SSOP, 56-pin

QFN and 100-pin TQFP package options for the AT2LP. Refer

to the “Pin Diagrams” on page 3 for differences between the

68300C/01C and 68320C/321C pinouts for the 56-pin

packages. For information on the CY7C68300A pinout, refer

to the CY7C68300A data sheet that is found in the ’EZ-USB

AT2’ folder of the CY4615C reference design kit CD.

Table 1. AT2LP Pin Descriptions

Note: (Italic pin names denote pin functionality during CY7C68300A compatibility mode)

100

TQFP

56

QFN

56

SSOP

Pin Name

Pin

Type

Default State

at Startup

Pin Description

1 55 6 V

CC

PWR V

CC

. Connect to 3.3V power source.

2 56 7 GND GND Ground.

3 1 8 IORDY I

[1]

Input ATA control. Apply a 1k pull up to 3.3V.

4 2 9 DMARQ I

[1]

Input ATA control.

5

6

7

8

N/A N/A GND Ground.

9 3 10 AV

CC

PWR Analog V

CC

. Connect to V

CC

through the shortest path

possible.

10 4 11 XTALOUT Xtal Xtal 24 MHz crystal output. (See “XTALIN, XTALOUT” on

page 11).

11 5 12 XTALIN Xtal Xtal 24 MHz crystal input. (See “XTALIN, XTALOUT” on

page 11).

12 6 13 AGND GND Analog ground. Connect to ground with as short a

path as possible.

13

14

15

N/A N/A NC No connect.

16 7 14 V

CC

PWR V

CC

. Connect to 3.3V power source.

17 8 15 DPLUS IO Hi-Z USB D+ signal (See “DPLUS, DMINUS” on page 11).

18 9 16 DMINUS IO Hi-Z USB D–signal (See “DPLUS, DMINUS” on page 11).

19 10 17 GND GND Ground.

20 11 18 V

CC

PWR V

CC

. Connect to 3.3V power source.

21 12 19 GND GND Ground.

22 N/A N/A SYSIRQ I Input USB interrupt request. (See “SYSIRQ” on page 12).

Active HIGH. Connect to GND if functionality is not

used.

23

24

25

N/A N/A GND GND Ground.

26

[3]

13

[3]

20 PWR500#

[2]

(PU 10K)

O bMaxPower request granted indicator. (See

“PWR500#” on page 14). Active LOW.

N/A for CY7C68320C/CY7C68321C 56-pin packages.

27 14 21 GND (RESERVED) Reserved. Tie to GND.

28 N/A N/A NC No connect.

29 15 22 SCL O Active for

several ms at

startup.

Clock signal for I

2

C interface. (See “SCL, SDA” on

page 11). Apply a 2.2k pull up resistor.

Notes

1. If byte 8, bit 4 of the EEPROM is set to ‘0’, the ATA interface pins are only active when VBUS_ATA_EN is asserted. See

“VBUS_ATA_ENABLE” on

page 14

.

2. A ‘#’ sign after the pin name indicates that it is active LOW.

[+] Feedback