Beep Codes

When errors occur during a boot routine that cannot be reported on the monitor, the computer may emit a beep code that identifies the problem. The beep

code is a pattern of sounds: for example, one beep followed by a second beep, then followed by a burst of three beeps (code 1-1-3) means that the computer

was unable to read the data in nonvolatile random-access memory (NVRAM). If the system loses power and beeps constantly when you turn it back on, the

BIOS is probably corrupted.

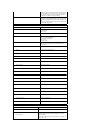

1 - On

2 - Off

3 - On

4 - On

Possible system board resource and/or system board hardware failure.

1 - On

2 - On

3 - Off

4 - Off

Possible system resource configuration error.

1 - On

2 - On

3 - On

4 - Off

Other failure.

1 - On

2 - On

3 - On

4 - On

End of POST - Hand off to boot.

1 - Off

2 - Off

3 - Off

4 - Off

The system is in a normal operating condition after POST.

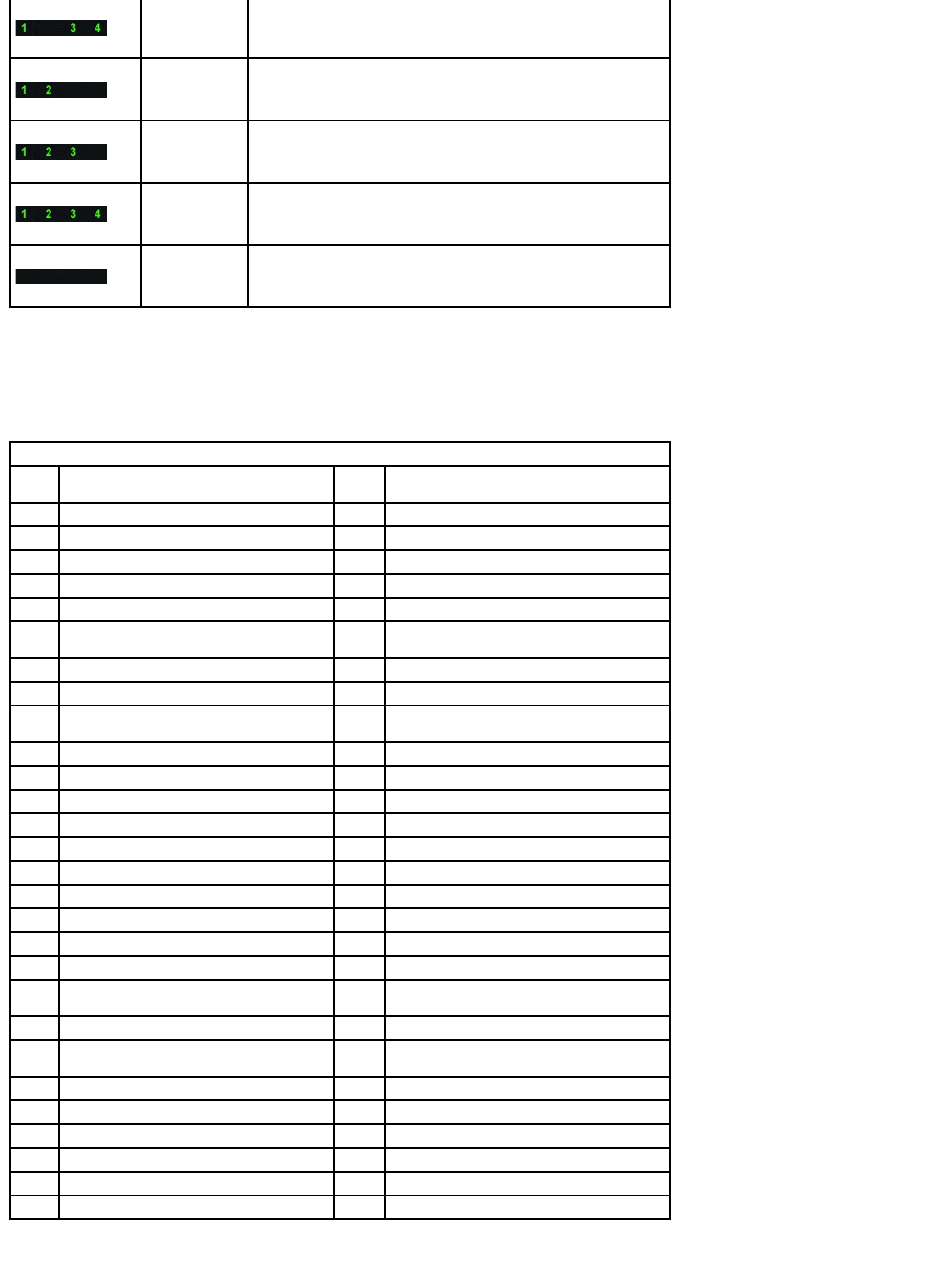

System Beep Codes

Beep

Code

Description

Beep

Code

Description

1-1-2

CPU register test in progress

2-4-3

1st 64 K RAM chip or data line failure - bit E

1-1-3

CMOS read/write test in progress or failure

2-4-4

1st 64 K RAM chip or data line failure - bit F

1-1-4

BIOS ROM checksum in progress or failure

3-1-1

Slave DMA register test in progress or failure

1-2-1

Timer Test in progress or failure

3-1-2

Master DMA register test in progress or failure

1-2-2

DMA initialization in progress or failure

3-1-3

Master IMR test in progress or failure

1-2-3

DMA page register read/write test in

progress or failure

3-1-4

Slave IMR test in progress or failure

1-3-1

RAM refresh verification in progress or failure

3-2-2

Interrupt vector loading in progress

1-3-2

1st 64 K RAM test in progress or failure

3-2-4

Keyboard controller test in progress or failure

1-3-3

1st 64 K RAM chip or data line failure (multi

bit)

3-3-1

CMOS power fail and checksum test in

progress

1-3-4

1st 64 K RAM odd/even logic failure

3-3-2

CMOS Config info validation in progress

1-4-1

1st 64 K RAM address line failure

3-3-3

RTC/Keyboard controller not found

1-4-2

1st 64 K RAM parity test in progress or failure

3-3-4

Screen memory test in progress or failure

1-4-3

Fail-safe timer test in progress

3-4-1

Screen initialization test in progress or failure

1-4-4

Software NMI port test in progress

3-4-2

Screen retrace tests test in progress or failure

2-1-1

1st 64 K RAM chip or data line failure - bit 0

3-4-3

Search for video ROM in progress

2-1-2

1st 64 K RAM chip or data line failure - bit 1

4-2-1

Timer tick interrupt test in progress or failure

2-1-3

1st 64 K RAM chip or data line failure - bit 2

4-2-2

Shutdown test in progress or failure

2-1-4

1st 64 K RAM chip or data line failure - bit 3

4-2-3

Gate A20 failure

2-2-1

1st 64 K RAM chip or data line failure - bit 4

4-2-4

Unexpected interrupt in Protected Mode

2-2-2

1st 64 K RAM chip or data line failure - bit 5

4-3-1

RAM test in progress or failure above address

0FFFFh

2-2-3

1st 64 K RAM chip or data line failure - bit 6

4-3-2

No memory in Bank 0

2-2-4

1st 64 K RAM chip or data line failure - bit 7

4-3-3

Interval Timer Channel 2 test in progress or

failure

2-3-1

1st 64 K RAM chip or data line failure - bit 8

4-3-4

Time-Of-Day Clock test in progress or failure

2-3-2

1st 64 K RAM chip or data line failure - bit 9

4-4-1

Super I/O chip failure

2-3-3

1st 64 K RAM chip or data line failure - bit A

4-4-4

Cache test failure

2-3-4

1st 64 K RAM chip or data line failure - bit B

2-4-1

1st 64 K RAM chip or data line failure - bit C

2-4-2

1st 64 K RAM chip or data line failure - bit D