RX

-

8581

SA

/

JE

/

NB

Page - 8 MQ372-02

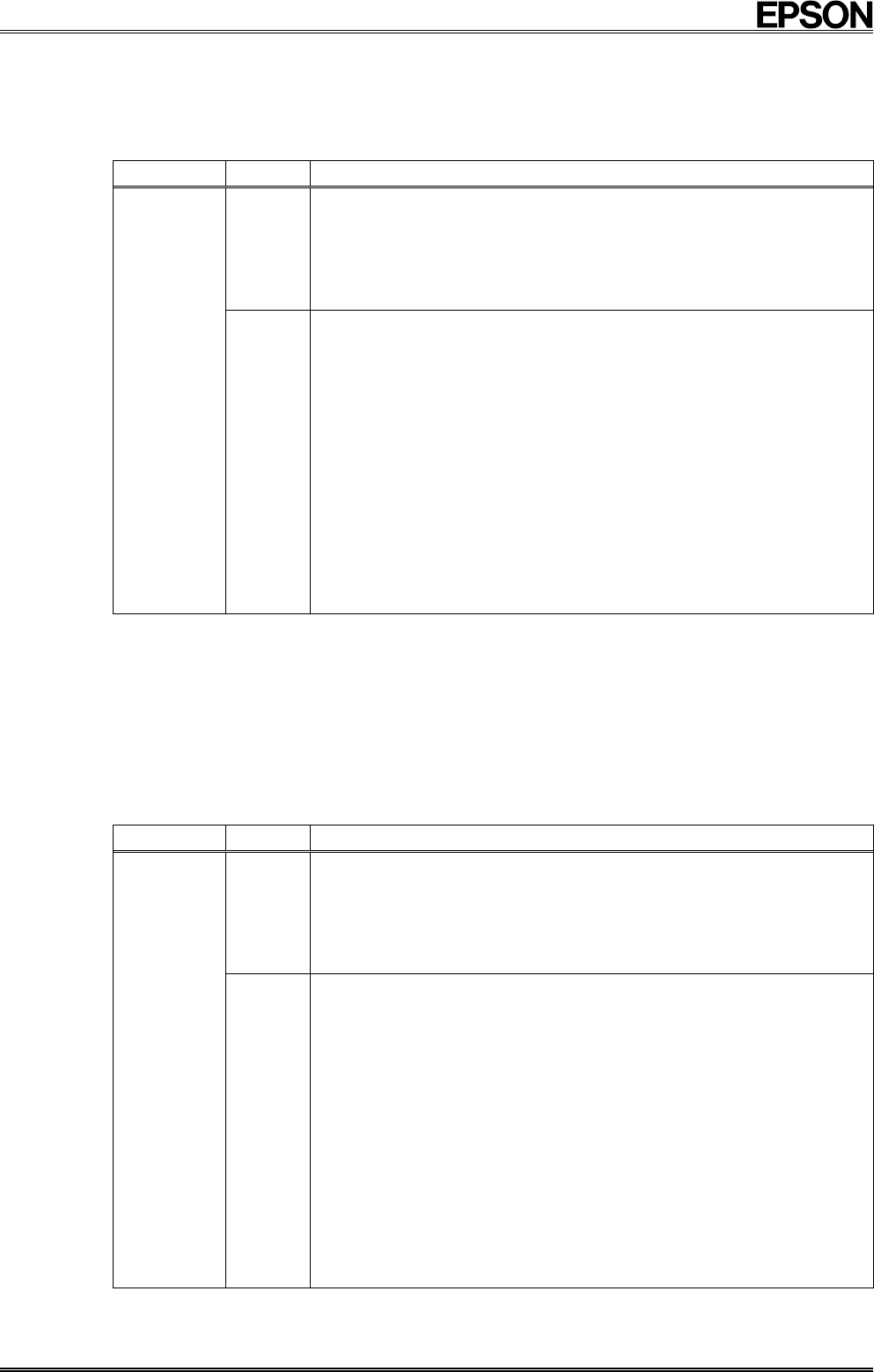

4) STOP bit

This bit is used to stop functions related to the RTC's internal counter operations.

Writing a "1" to this bit stops the counter operations.

Writing a "0" to this bit cancels stop status (restarts operations).

∗ For optimum performance, do not use this bit for functions other than the clock and calendar functions.

STOP

Data Description

0

[Normal operation mode]

This bit is used to cancel stop status for (i.e., restart) the clock and calendar

function. Also, when "1" is written to the STOP bit, it cancels stop status for

the fixed-cycle timer function.

∗

When the RESET bit value is "1" operation will not be restarted. To restart operation, a "0" must

be written to both the STOP bit and the RESET bit.

Write/Read

1

[Operation stop mode]

Stops updating of year, month, date, day, hour, minute, and second values

and partially stops the fixed-cycle timer function.

(Stop 1) Stops updating of year, month, date, day, hour, minute, and

second values

• This stops all clock and calendar update operations.

Once this occurs, no more time update interrupt events or alarm

interrupt events occur.

(Stop 2) Partially stops the fixed-cycle timer function

• If the fixed-cycle timer's source clock settings include an update

setting of 64 Hz, 1 Hz, or "Minute", the fixed-cycle timer function does

not operate.

∗

However, this function does operate

when the fixed-cycle timer's source

clock setting is 4096 Hz.

When this bit value is "1", internal divider stops from 2048Hz to 1 Hz .

5) RESET bit

Like the STOP function described above, this function stops functions related to counter operations. It also

resets the RTC module's internal counter value when the value is less than one second.

Writing a "1" to this bit stops the counter operation and resets the RTC module's internal counter value when the

value is less than one second.

Writing a "0" to this bit cancels stop status for (restarts) these operations. If a STOP condition or repeated

START condition is received while the 0.95-second bus timeout function is operating, stop status is automatically

canceled (the RESET bit value is changed from "1" to "0").

∗ For optimum performance, do not use this bit for functions other than the clock and calendar functions.

RESET

Data Description

0

[Normal operation mode]

This bit is used to cancel stop status for (i.e., restart) the clock and calendar

function. Also, when "1" is written to the RESET bit, it cancels stop status for

the fixed-cycle timer function.

∗

Since operation is not restarted when the STOP bit value is "1", to restart operation, a "0" must be

written to both the STOP bit and the RESET bit.

Write/Read

1

[Operation stop mode]

Stops updating of year, month, date, day, hour, minute, and second values

and partially stops the fixed-cycle timer function.

(Stop 1) Stops updating of year, month, date, day, hour, minute, and

second values

• This stops all clock and calendar update operations.

Once this occurs, no more time update interrupt events or alarm

interrupt events occur.

(Stop 2) Partially stops the fixed-cycle timer function

• If the fixed-cycle timer's source clock settings include an update

setting of 64 Hz, 1 Hz, or "Minute", the fixed-cycle timer function does

not operate.

∗

However, this function does operate when the fixed-cycle timer's source clock setting is

4096 Hz.

(Note) When this bit value is "1", the internal divider keeps the reset state, from 2048Hz to 1 Hz .