RX

-

8581

SA

/

JE

/

NB

Page - 23 MQ372-02

8.6.4. Data transfers and acknowledge responses during I

2

C-BUS communications

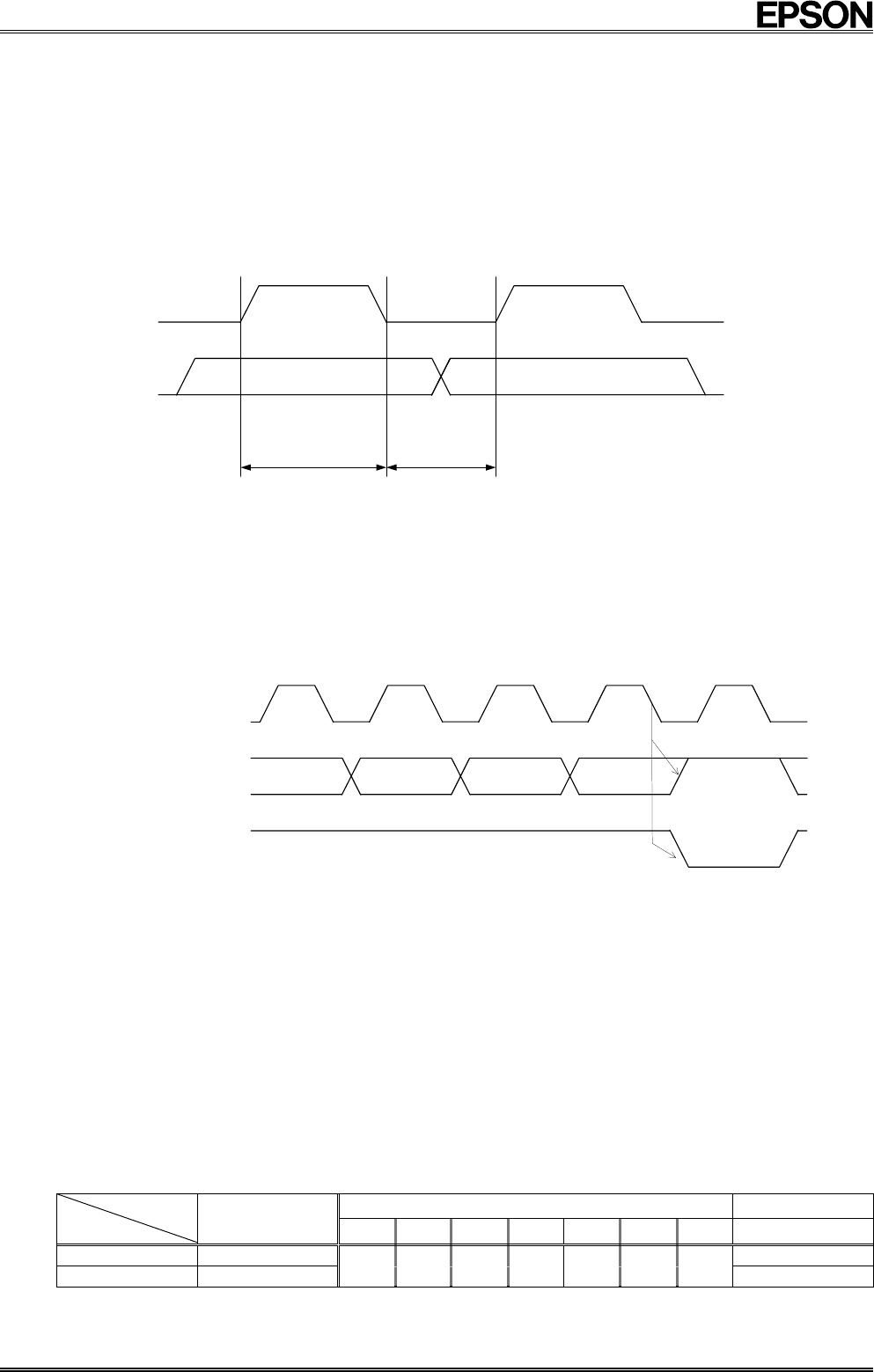

1) Data transfers

Data transfers are performed in 8-bit (1 byte) units once the START condition has occurred. There is no limit

on the amount (bytes) of data that are transferred between the START condition and STOP condition.

(However, the transfer time must be no longer than 0.95 seconds.)

The address auto increment function operates during both write and read operations.

After address Fh, incrementation goes to address 0h.

Updating of data on the transmitter (transmitting side)'s SDA line is performed while the SCL line is at low

level. The receiver (receiving side) receives data while the SCL line is at high level.

SCL

Data is valid

when data line is

stable

SDA

Data can be

changed

∗ Note with caution that if the SDA data is changed while the SCL line is at high level, it will be treated as a

START, RESTART, or STOP condition.

2) Data acknowledge response (ACK signal)

When transferring data, the receiver generates a confirmation response (ACK signal, low active) each time an

8-bit data segment is received. If there is no ACK signal from the receiver, it indicates that normal

communication has not been established. (This does not include instances where the master device intentionally

does not generate an ACK signal.)

Immediately after the falling edge of the clock pulse corresponding to the 8th bit of data on the SCL line, the

transmitter releases the SDA line and the receiver sets the SDA line to low (= acknowledge) level.

SCL from Master

SDA from transmitter (sending

side)

ACK signal

1

2

8

9

SDA from receiver (receiving

side)

Release SDA

Low active

After transmitting the ACK signal, if the Master remains the receiver for transfer of the next byte, the SDA is

released at the falling edge of the clock corresponding to the 9th bit of data on the SCL line. Data transfer

resumes when the Master becomes the transmitter.

When the Master is the receiver, if the Master does not send an ACK signal in response to the last byte sent

from the slave, that indicates to the transmitter that data transfer has ended. At that point, the transmitter

continues to release the SDA and awaits a STOP condition from the Master.

8.6.5. Slave address

The I

2

C bus device does not include a chip select pin such as is found in ordinary logic devices. Instead of using a

chip select pin, slave addresses are allocated to each device.

All communications begin with transmitting the [START condition] + [slave address (+ R/W specification)]. The

receiving device responds to this communication only when the specified slave address it has received matches its

own slave address.

Slave addresses have a fixed length of 7 bits. This RTC's slave address is [1010

001∗

∗∗

∗].

An R/W bit ("*" above) is added to each 7-bit slave address during 8-bit transfers.

Slave address R/W bit

Transfer data

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

Read

A3 h

1 (= Read)

Write

A2 h

1 0 1 0 0 0 1

0 (= Write)