MB3887

5

■

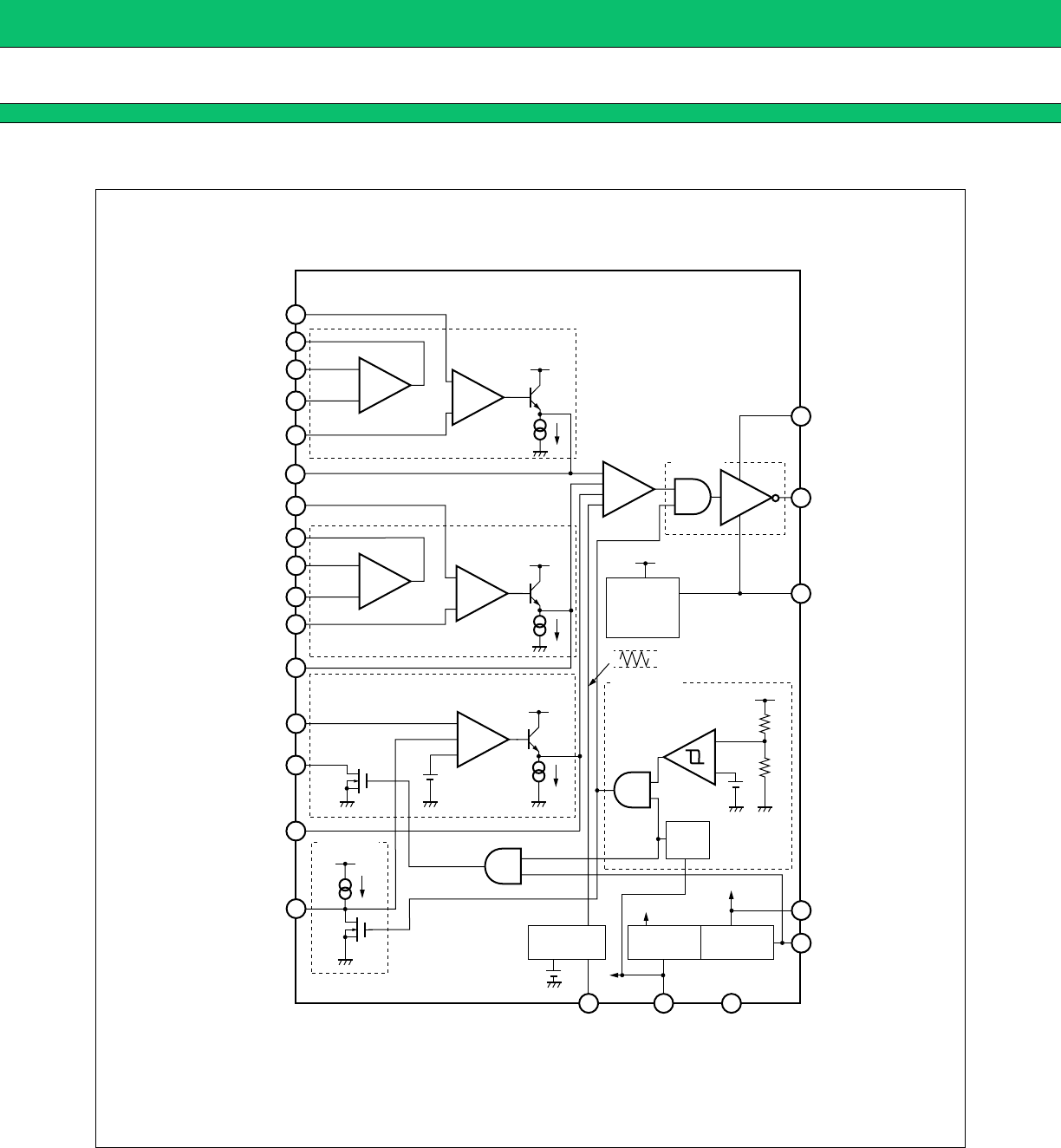

BLOCK DIAGRAM

+

−

−

+

8

10

13

12

9

+

−

−

+

4

2

24

1

3

× 20

× 20

+

+

+

−

5

20

21

19

−

+

+

+

−

11

16

22

17 6 23

14

18

<Current Amp1>

<Error Amp1>

7

VREF

<Current Amp2>

<Error Amp2>

VREF

<Error Amp3>

VREF

VREF

VREF

5.0 V

4.2 V

10

µA

15

<SOFT>

2.5 V

1.5 V

<OUT>

<UVLO>

<OSC>

Bias

Voltage

<VH>

<REF> <CTL>

<PWM Comp.>

Drive

VCC

(V

CC − 6 V)

(VCC UVLO)

VCC

VCC

VCC

CTL

215 kΩ

35 kΩ

0.91 V

(0.77 V)

VREF

UVLO

4.2 V

bias

−INC2

OUTD

FB2

OUTC2

VREF

−INE2

+INE2

+INE1

FB1

OUTC1

−INE1

−INC1

+INC2

GND

CS

VCC (O)

OUT

VH

RT

−INE3

FB3

+INC1

45 pF