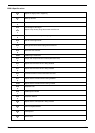

Chapter 4 161

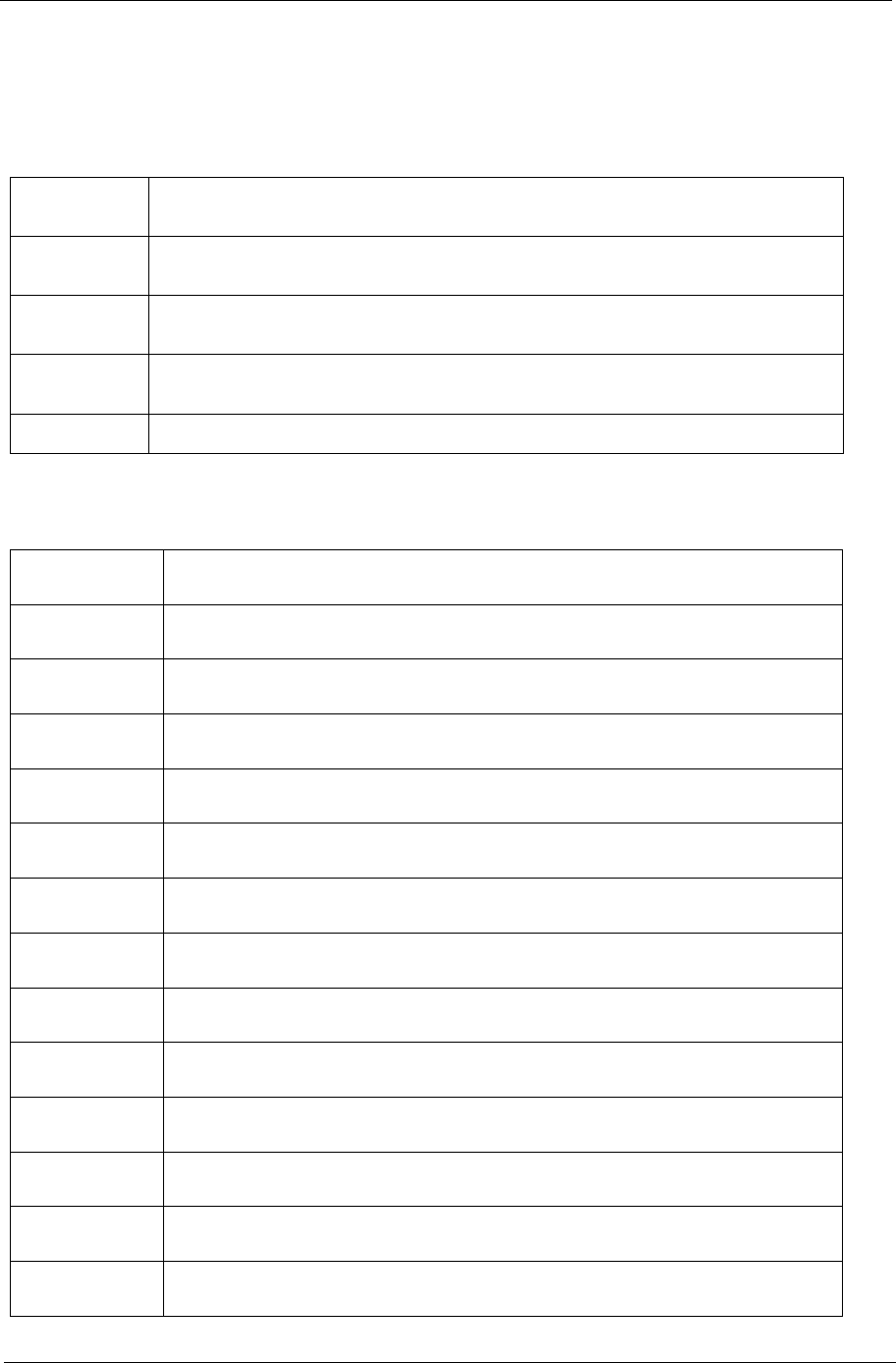

Post Codes

These tables describe the Post Codes and components of the POST process.

Sec:

NO_EVICTION_MODE_DEBUG EQU 1 (CommonPlatform\sec\Ia32\SecCore.inc)

Memory:

DEBUG_BIOS EQU 1 (Chipset\Alviso\MemoryInitAsm\IA32\IMEMORY.INC)

0x

C2

MTRR setup

0x

C3

Enable cache

0x

C4

Establish cache tags

0x

C5

Enter NEM, Place the BSP in No Fill mode, set CR0.CD = 1, CR0.NW = 0.

0xCF Cache Init Finished

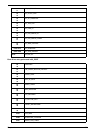

0x

A0

First memory check point

0x

01

Enable MCHBAR

0x

02

Check for DRAM initialization interrupt and reset fail

0x

03

Verify all DIMMs are DDR or DDR2 and unbuffered

0x

04

Detect an improper warm reset and handle

0x

05

Detect if ECC SO-DIMMs are present in the system

0x

06

Verify all DIMMs are single or double sided and not asymmetric

0x

07

Verify all DIMMs are x8 or x16 width

0x

08

Find a common CAS latency between the DIMMS and the MCH

0x

09

Determine the memory frequency and CAS latency to program

0x

10

Determine the smallest common TRAS for all DIMMs

0x

11

Determine the smallest common TRP for all DIMMs

0x

12

Determine the smallest common TRCD for all DIMMs

0x

13

Determine the smallest refresh period for all DIMMs