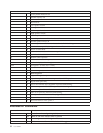

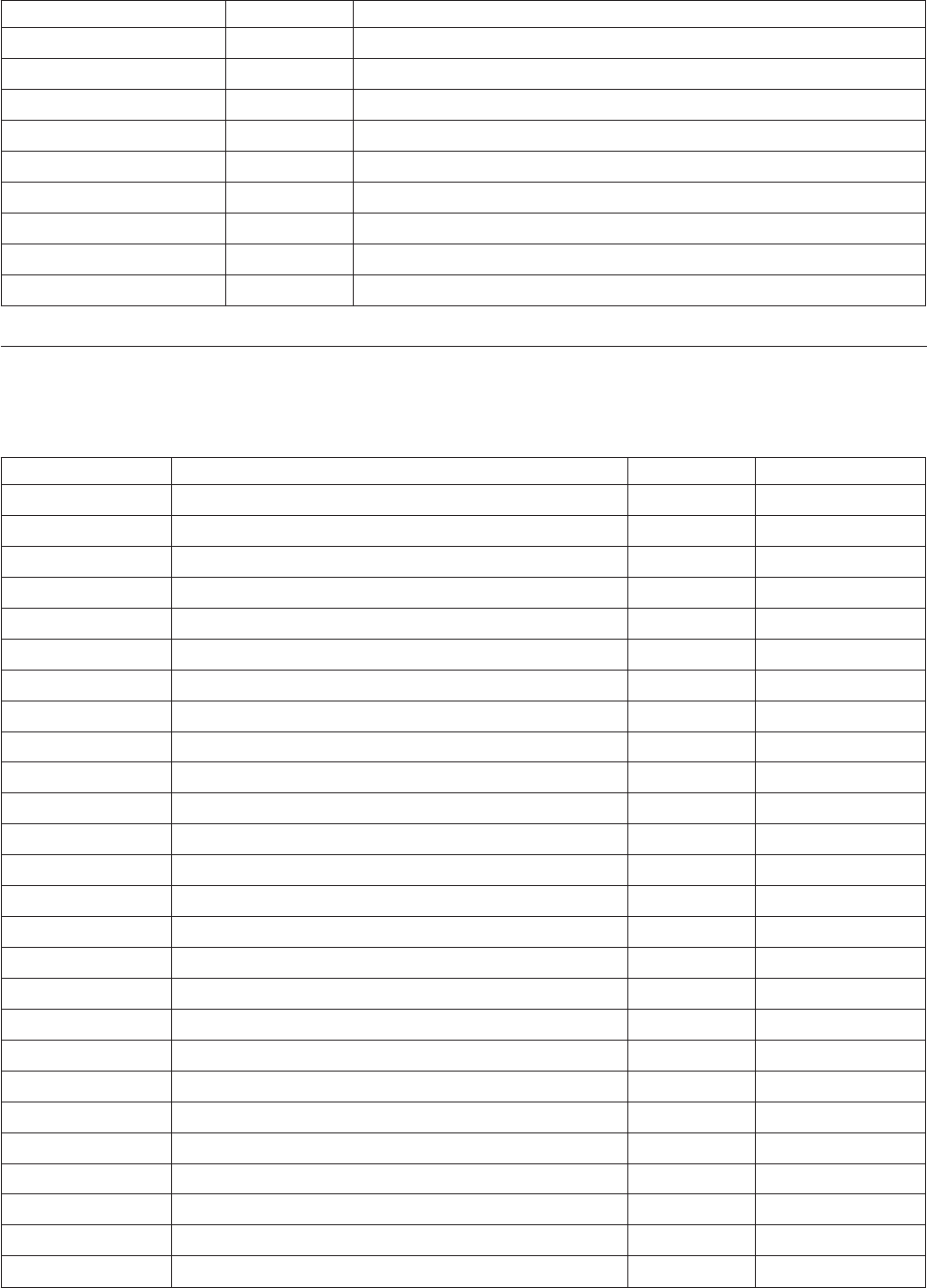

Address range (hex) Size (bytes) Description

03F8 – 03FF 8 COM1

0400 – 047F 128 Available

0480 – 048F 16 DMA channel high page registers

0490 – 0CF7 1912 Available

0CF8 – 0CFB 4 PCI configuration address register

0CFC – 0CFF 4 PCI configuration data register

LPTn + 400h 8 ECP port, LPTn base address + hex 400

OCF9 1 Turbo and reset control register

0D00 – FFFF 62207 Available

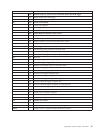

DMA I/O address map

The following table lists resource assignments for the DMA address map. Any

addresses that are not shown are reserved.

Address (hex) Description Bits Byte pointer

0000 Channel 0, memory address register 00 – 15 Yes

0001 Channel 0, transfer count register 00 – 15 Yes

0002 Channel 1, memory address register 00 – 15 Yes

0003 Channel 1, transfer count register 00 – 15 Yes

0004 Channel 2, memory address register 00 – 15 Yes

0005 Channel 2, transfer count register 00 – 15 Yes

0006 Channel 3, memory address register 00 – 15 Yes

0007 Channel 3, transfer count register 00 – 15 Yes

0008 Channels 0–3, read status/write command register 00 – 07

0009 Channels 0–3, write request register 00 – 02

000A Channels 0–3, write single mas register bits 00 – 02

000B Channels 0–3, mode register (write) 00 – 07

000C Channels 0–3, clear byte pointer (write) N/A

000D Channels 0–3, master clear (write)/temp (read) 00 – 07

000E Channels 0-3, clear mask register (write) 00 – 03

000F Channels 0-3, write all mask register bits 00 – 03

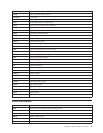

0081 Channel 2, page table address register 00 – 07

0082 Channel 3, page table address register 00 – 07

0083 Channel 1, page table address register 00 – 07

0087 Channel 0, page table address register 00 – 07

0089 Channel 6, page table address register 00 – 07

008A Channel 7, page table address register 00 – 07

008B Channel 5, page table address register 00 – 07

008F Channel 4, page table address/refresh register 00 – 07

00C0 Channel 4, memory address register 00 – 15 Yes

00C2 Channel 4, transfer count register 00 – 15 Yes

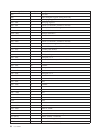

Appendix C. System address maps 39