The engine of growth for your emerging businesses.

Please see the Legal Information section for important notices and information.

4

Turbo Boost Technology dynamically turns off unused processor cores and increases the clock speed of

the cores in use, by up to two model frequencies. For example, with three cores active, a 2.26GHz

processor can run the cores at 2.4GHz. With only one or two cores active, the same processor can run

those cores at 2.53GHz. Similarly, a 2.93GHz processor can run at 3.06GHz or even 3.33GHz. When the

cores are needed again, they are dynamically turned back on and the processor frequency is adjusted

accordingly.

Intelligent Power Capability powers individual processor elements on and off as needed, to reduce

power draw.

Execute Disable Bit functionality can help prevent certain classes of malicious buffer overflow attacks

when combined with a supporting operating system.

DDR

-

3 Registe

red Memory with Chipkill ECC Protection

The x3400 M2 ships with registered double data rate III (DDR-3) memory and provides Active Memory

features, including advanced Chipkill memory protection (optionally), for up to 16X better error correction

than standard ECC memory. In addition to offering better performance than DDR-2 or fully-buffered

memory, DDR-3 memory also uses less energy. DDR-2 memory already offered up to 37% lower energy

use than fully buffered memory. Now, a generation later, DDR-3 memory is even more efficient, using 22%

less energy than DDR-2 memory.

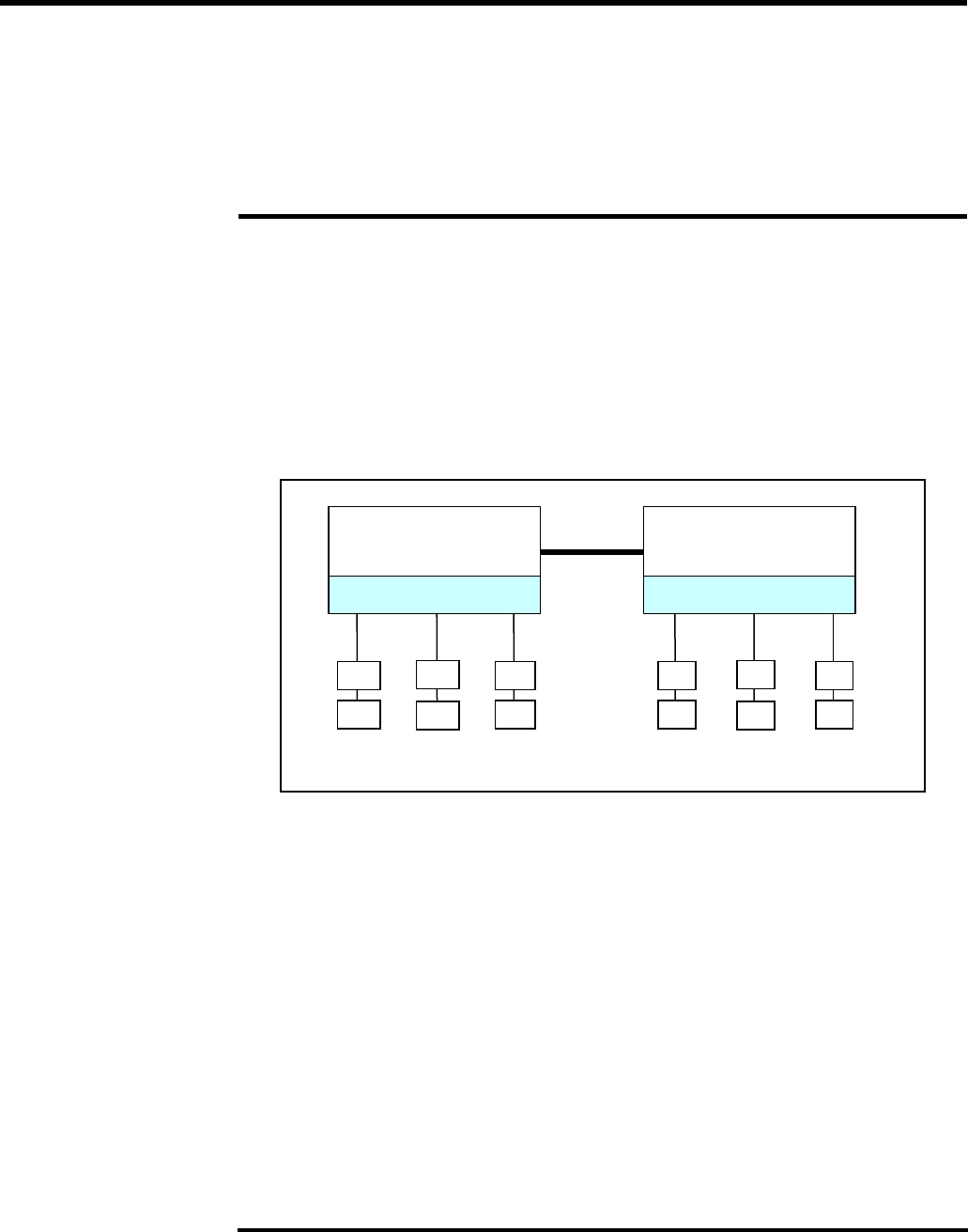

The x3400 M2 supports up to 96GB of memory in twelve DIMM slots. Redesign in the architecture of the

Xeon 5500 series processors bring radical changes in the way memory works in these servers. For

example, the Xeon 5500 series processor integrates the memory controller inside the processor,

resulting in two memory controllers in a 2-socket system. Each memory controller has three memory

channels. Depending on the type of memory, population of memory, and processor model, the memory

may be clocked at 1066MHz or 800MHz.

Note: If only one processor is installed, only the first six DIMM slots can be used. Adding a second

processor not only doubles the amount of memory available for use, but also doubles the number of

memory controllers, thus doubling the system memory bandwidth. If you add a second processor, but no

additional memory for the second processor, the second processor has to access the memory from the

first processor “remotely,” resulting in longer latencies and lower performance. The latency to access

remote memory is almost 75% higher than local memory access. So, the goal should be to always

populate both processors with memory.

The E552x-and-up models support up to 1066MHz clock speed, and the E550x models support 800MHz

clock speed. Using 1066MHz memory (where supported) versus 800MHz offers up to 28% better

performance.

Xeon 5550 series processors access memory with almost 50% lower latency than the previous

generation 5400 series processors. That can result in faster processing of latency-sensitive workloads.

This new processor design comes with some trade-offs in memory capacity, performance, and cost: For

example, greater memory capacity comes with lower memory speed. Alternatively, it is possible to

achieve the same memory capacity at lower cost but at a lower memory speed.

Regardless of memory speed, the Xeon 5500 platform represents a significant improvement in memory

bandwidth over the previous Xeon 5400 platform. This improvement is mainly due to the dual integrated

memory controllers and faster DDR-3 memory. Throughput at 800MHz is 25 gigabytes per second

(GBps), and at 1066MHz it’s 32GBps. This improvement translates into improved application performance

and scalability.

Memory interleaving refers to how physical memory is interleaved across the physical DIMMs. A balanced

system provides the best interleaving. A Xeon 5500 processor-based system is balanced when all

Ch2

Ch1

Ch0

Ch2

Ch1

Ch0

Xeon 5500

Processor 0

Memory Controller

4

1

6

3

5

2

Xeon 5500

Processor 1

12

9

QPI

Memory Controller

10

7

11

8

D2

D3

D5

D6

D7

D8

D10

D11

D13

D14

D15

D16

1-12: DIMM population sequence; D1-D12: DIMM slot assignments