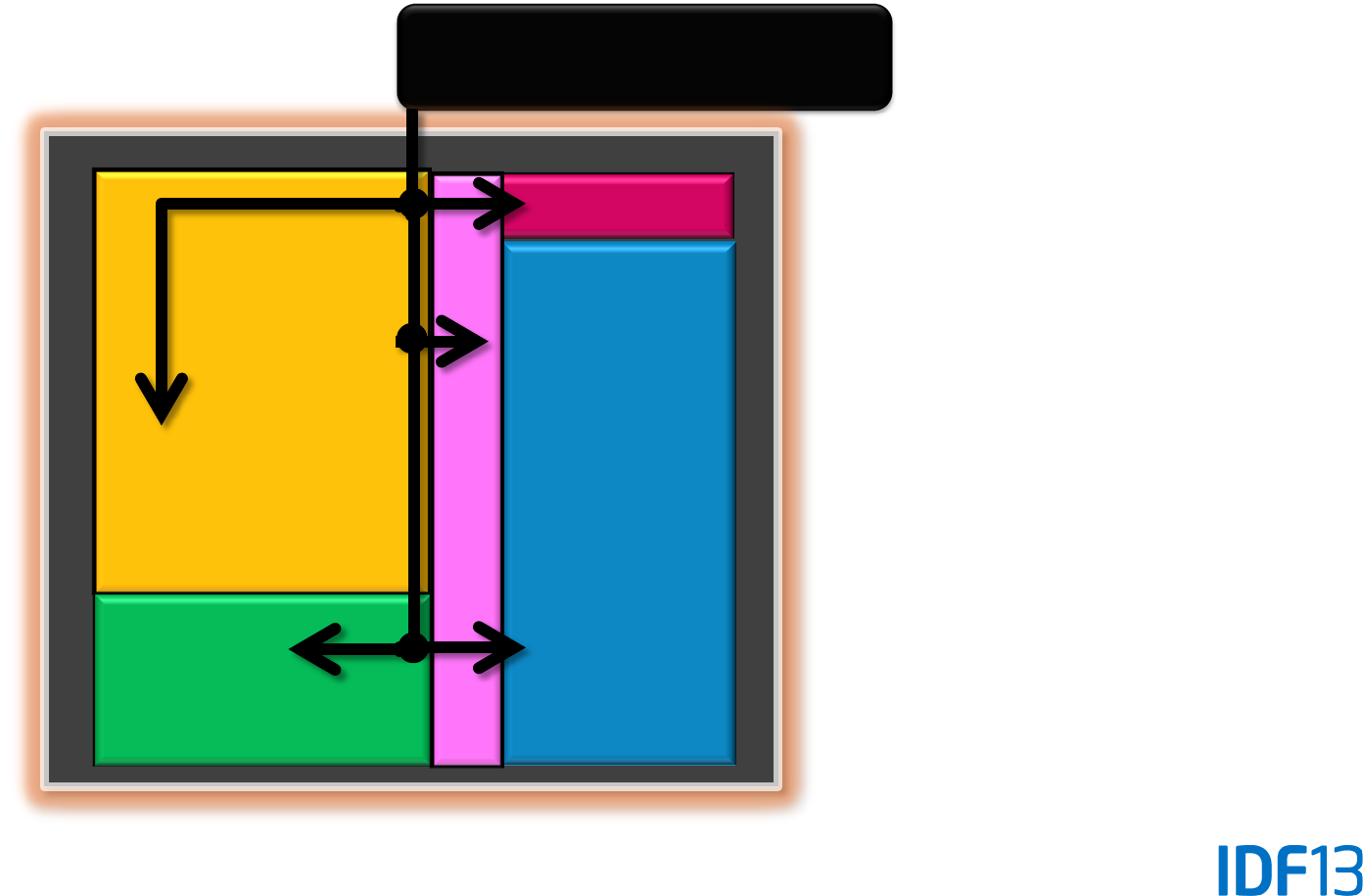

20

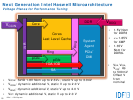

BCLK @100, 125 or 167

MHz +/1 5-7%

DDR

Cores

Last Level

Cache

System

Agent

PCIe

*

DMI

pGfx

Next Generation Intel Haswell Microarchitecture

Clock Tree

• Single BCLK input comes

from PCH in <1MHz steps

• Acceptable input to CPU

limited by PIC Express

*

(PCIe) and DMI PLL interface:

100MHz x ±5-7% PEG/DMI @ 5:5

125MHz x ±5-7% PEG/DMI @ 5:4

167MHz x ±5-7% PEG/DMI @ 5:3

• Frequency Relationships

f(GT) = BCLK/2*GT Ratio

f(Core) = BCLK*Core Ratio

f(Ring) = BCLK*Ring Ratio

f(DDR) = BCLK*1.33*DDR Ratio

-Or-

f(DDR) = BCLK*1.00*DDR Ratio

Ring